GR712RC-UM, Jun 2017, Version 2.9 125 www.cobham.com/gaisler

GR712RC

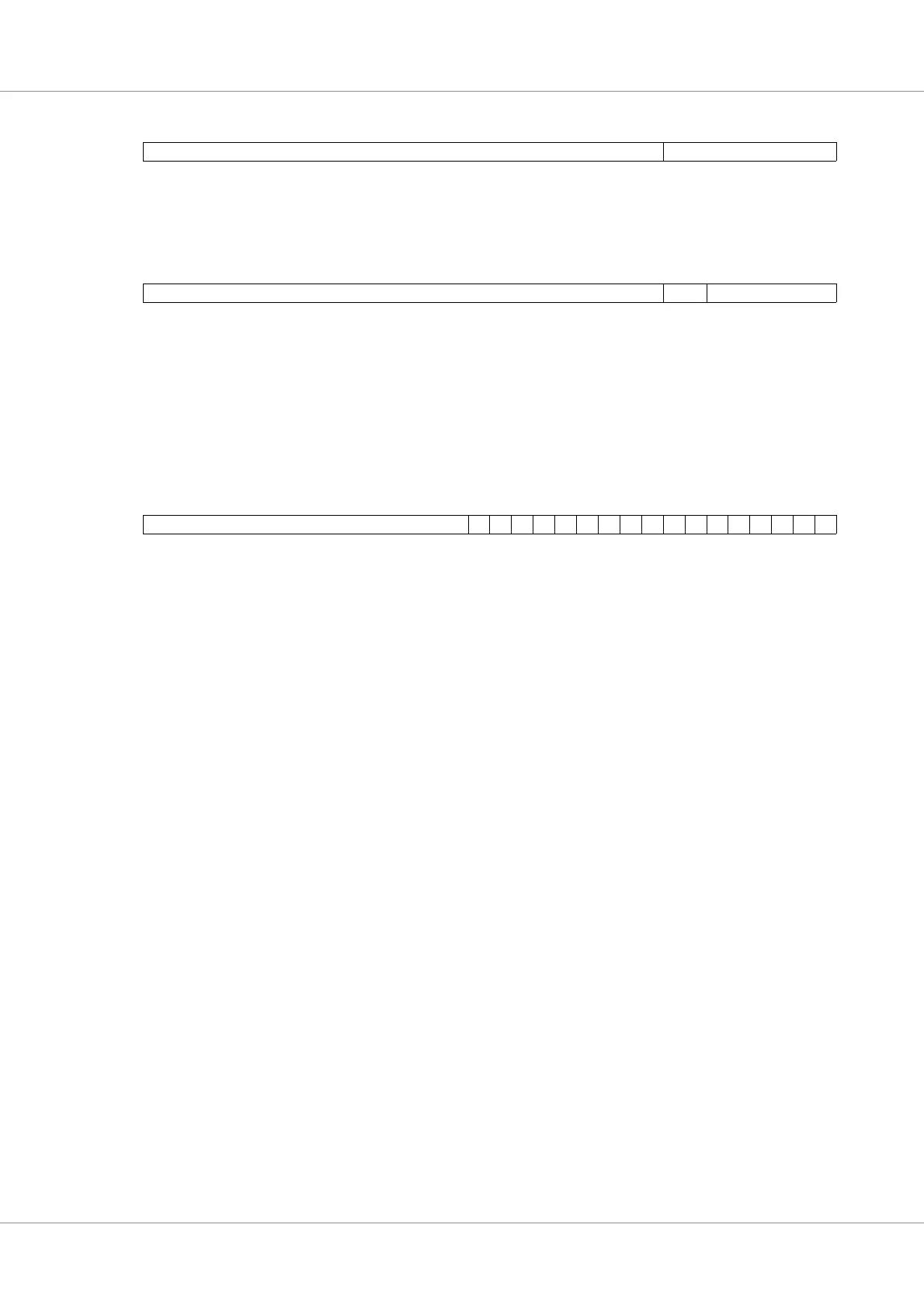

Table 98. GRSPW destination key

31 87 0

RESERVED DESTKEY

31: 8 RESERVED

7: 0 Destination key (DESTKEY) - RMAP destination key. Reset value: 0.

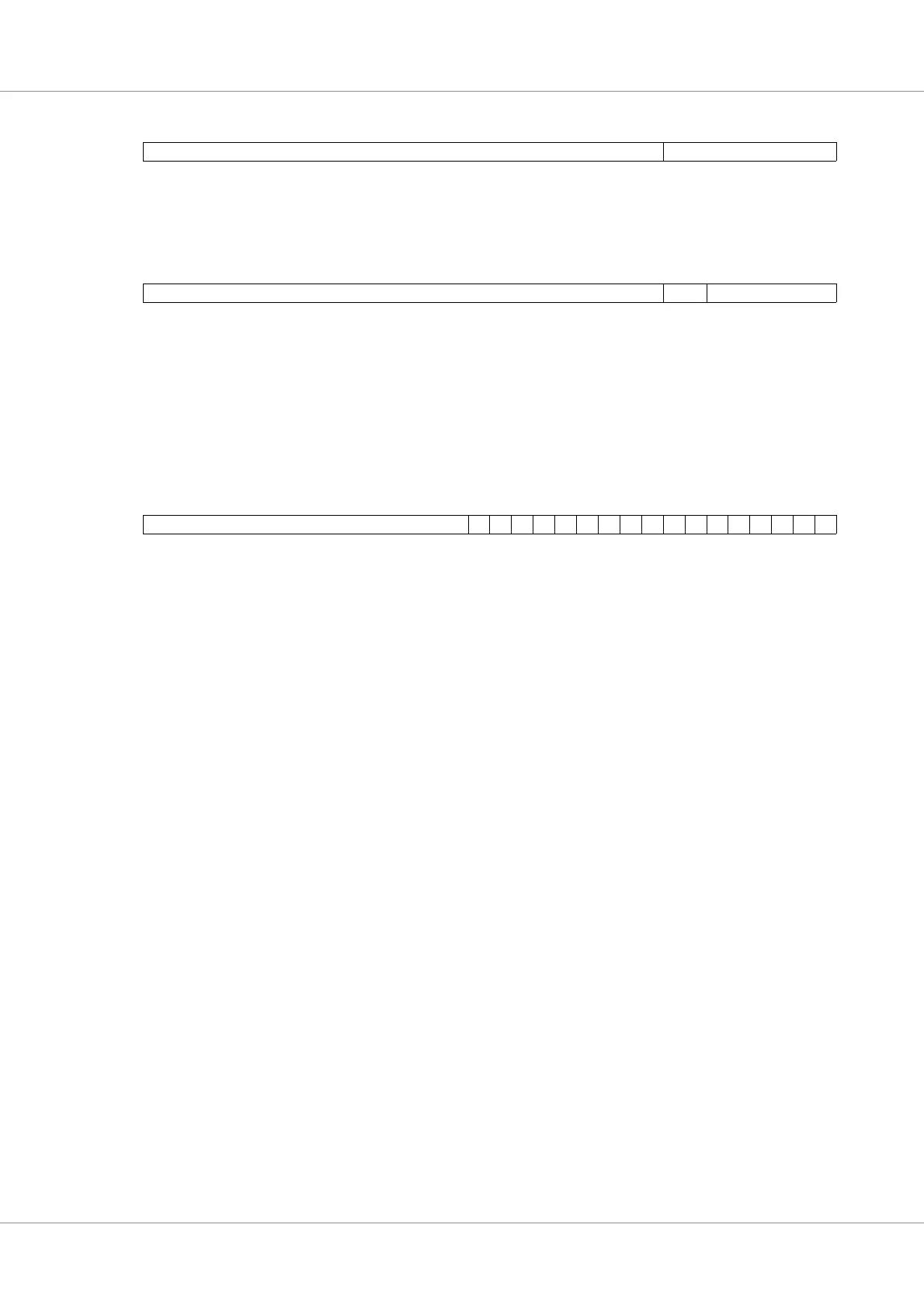

Table 99. GRSPW time register

31 8765 0

RESERVED TCTRL TIMECNT

31: 8 RESERVED

7: 6 Time control flags (TCTRL) - The current value of the time control flags. Sent with time-code

resulting from a tick-in. Received control flags are also stored in this register. Reset value: ‘0’.

5: 0 Time counter (TIMECNT) - The current value of the system time counter. It is incremented for each

tick-in and the incremented value is transmitted. The register can also be written directly but the

written value will not be transmitted. Received time-counter values are also stored in this register.

Reset value: ‘0’.

Table 100. GRSPW dma control register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RESERVED LE SP SA EN NS RD RX AT RA TA PR PS AI RI TI RE TE

31: 17 RESERVED

16 Link error disable (LE) - Disable transmitter when a link error occurs. No more packets will be trans-

mitted until the transmitter is enabled again. Reset value: ‘0’.

15 Strip pid (SP) - Remove the pid byte (second byte) of each packet. The address byte (first byte) will

also be removed when this bit is set independent of the SA bit. Reset value: ‘0’.

14 Strip addr (SA) - Remove the addr byte (first byte) of each packet. Reset value: ‘0’.

13 Enable addr (EN) - Enable separate node address for this channel. Reset value: ‘0’.

12 No spill (NS) - If cleared, packets will be discarded when a packet is arriving and there are no active

descriptors. If set, the GRSPW will wait for a descriptor to be activated.

11 Rx descriptors available (RD) - Set to one, to indicate to the GRSPW that there are enabled descrip-

tors in the descriptor table. Cleared by the GRSPW when it encounters a disabled descriptor: Reset

value: ‘0’.

10 RX active (RX) - Is set to ‘1’ if a reception to the DMA channel is currently active otherwise it is ‘0’.

Only readable.

9 Abort TX (AT) - Set to one to abort the currently transmitting packet and disable transmissions. If no

transmission is active the only effect is to disable transmissions. Self clearing. Reset value: ‘0’.

8 RX AHB error (RA) - An error response was detected on the AHB bus while this receive DMA

channel was accessing the bus. Cleared when written with a one. Reset value: ‘0’.

7 TX AHB error (TA) - An error response was detected on the AHB bus while this transmit DMA

channel was accessing the bus. Cleared when written with a one. Reset value: ‘0’.

6 Packet received (PR) - This bit is set each time a packet has been received. never cleared by the SW-

node. Cleared when written with a one. Reset value: ‘0’.

5 Packet sent (PS) - This bit is set each time a packet has been sent. Never cleared by the SW-node.

Cleared when written with a one. Reset value: ‘0’.

4 AHB error interrupt (AI) - If set, an interrupt will be generated each time an AHB error occurs when

this DMA channel is accessing the bus. Not reset.

3 Receive interrupt (RI) - If set, an interrupt will be generated each time a packet has been received, if

the interrupt enable (IE) bit in the corresponding receive descriptor is set as well. This happens both

if the packet is terminated by an EEP or EOP. Not reset.

2 Transmit interrupt (TI) - If set, an interrupt will be generated each time a packet is transmitted, if the

interrupt enable (IE) bit in the corresponding transmit descriptor is set as well. The interrupt is gener-

ated regardless of whether the transmission was successful or not. Not reset.

Loading...

Loading...