GR712RC-UM, Jun 2017, Version 2.9 49 www.cobham.com/gaisler

GR712RC

4.6.3 MMU registers

The following MMU registers are implemented:

The definition of the registers can be found in the SPARC V8 manual.

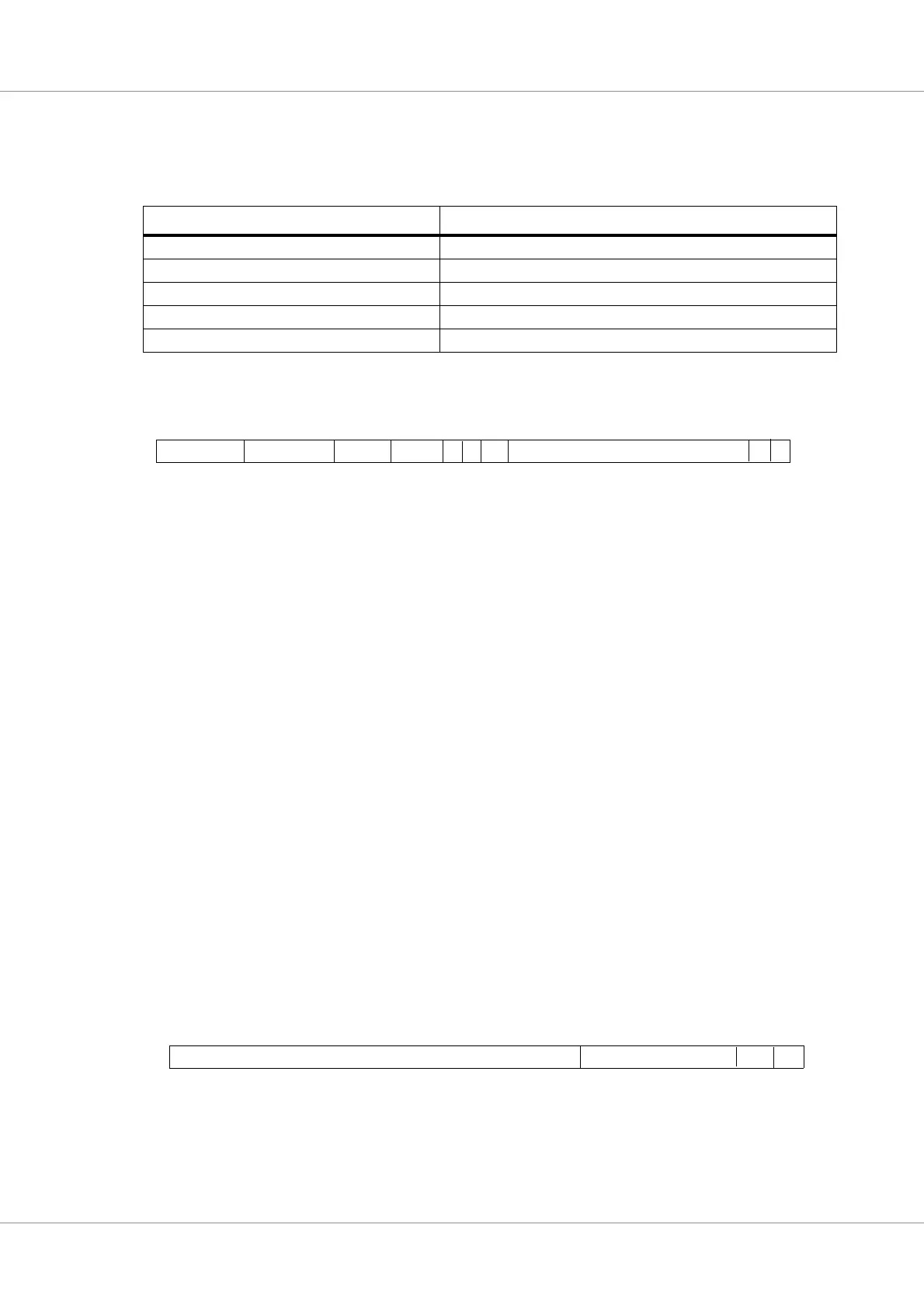

[31:28]: MMU Implementation ID. Hardcoded to “0000”.

[27:24]: MMU Version ID. Hardcoded to “0000”.

[23:21]: Number of ITLB entries. The number of ITLB entries is calculated as 2

ITLB

.

[20:18]: Number of DTLB entries. The number of DTLB entries is calculated as 2

DTLB

.

[17]: Separate TLB. Set to 1 to indicate that separate instructions and data TLBs are implemented.

[15]: TLB disable. When set to 1, the TLB will be disabled and each data access will generate an MMU page table walk.

[1]: No Fault. When NF= 0, any fault detected by the MMU causes FSR and FAR to be updated and causes a fault to be

generated to the processor. When NF= 1, a fault on an access to ASI 9 is handled as when NF= 0; a fault on an access

to any other ASI causes FSR and FAR to be updated but no fault is generated to the processor.

[0]: Enable MMU. 0 = MMU disabled, 1 = MMU enabled.

4.6.4 Translation look-aside buffer (TLB)

The MMU uses a separate 16-entry TLB for instructions and data accesses. The organisation of the

TLB and number of entries is not visible to the software and does thus not require any modification to

the operating system.

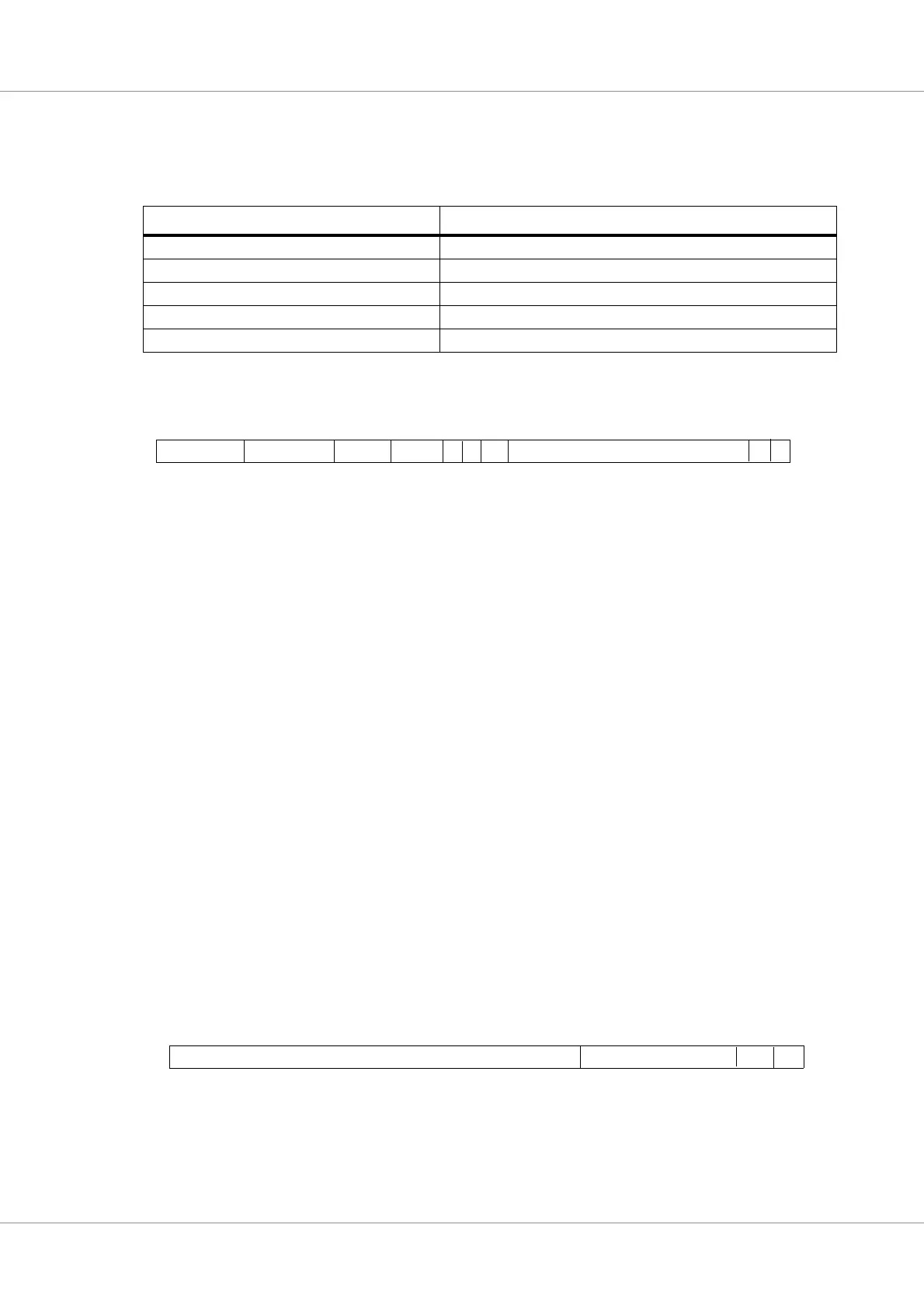

4.6.5 Snoop tag diagnostic access

To implement cache snooping, the MMU contains a separate snoop tag for each virtual tag. The tags

can be accessed via ASI 0x1E. This is primarily useful for RAM testing, and should not be performed

during normal operation. The figure below shows the layout of the snoop tag for the 4 KiB way in

data cache:

[31:12] Address tag. The physical address tag of the cache line.

[1]: Parity. The odd parity over the snoop tag (ATAG field.

[0]: Snoop hit. When set, the cache line is not valid and will cause a cache miss if accessed by the processor.

Table 20. MMU registers (ASI = 0x19)

Address Register

0x000 MMU control register

0x100 Context pointer register

0x200 Context register

0x300 Fault status register

0x400 Fault address register

Figure 10. MMU control register

01

2

1720

15

1631 18

DTLB

2123

ITLB

VER

IMPL

28

27 24

NF

E

RESERVED

TD

14

ST

-

Figure 11. Snoop cache tag layout

011 2

1

1231

ATA G

PAR HIT

“0000000000”

Loading...

Loading...