Size CCR Bit

Mnemonic Operation B/W N Z V C

Arith- EXTS (< Bit 7 > of < Rd >) B ↕↕00

metic → (< Bit 15 to 8 > of < Rd >)

opera- EXTU 0 → (<Bit 15 to 8 > of < Rd >) B 0 ↕ 00

tions TST (EAd) – 0, Set CCR B/W ↕↕00

NEG 0 – (EAd) → (EAd) B/W ↕↕0 ↕

CLR 0 → (EAd) B/W 0 1 0 0

TAS (EAd) – 0, Set CCR B ↕↕00

(1)

2

→ (< Bit 7 > of < EAd >)

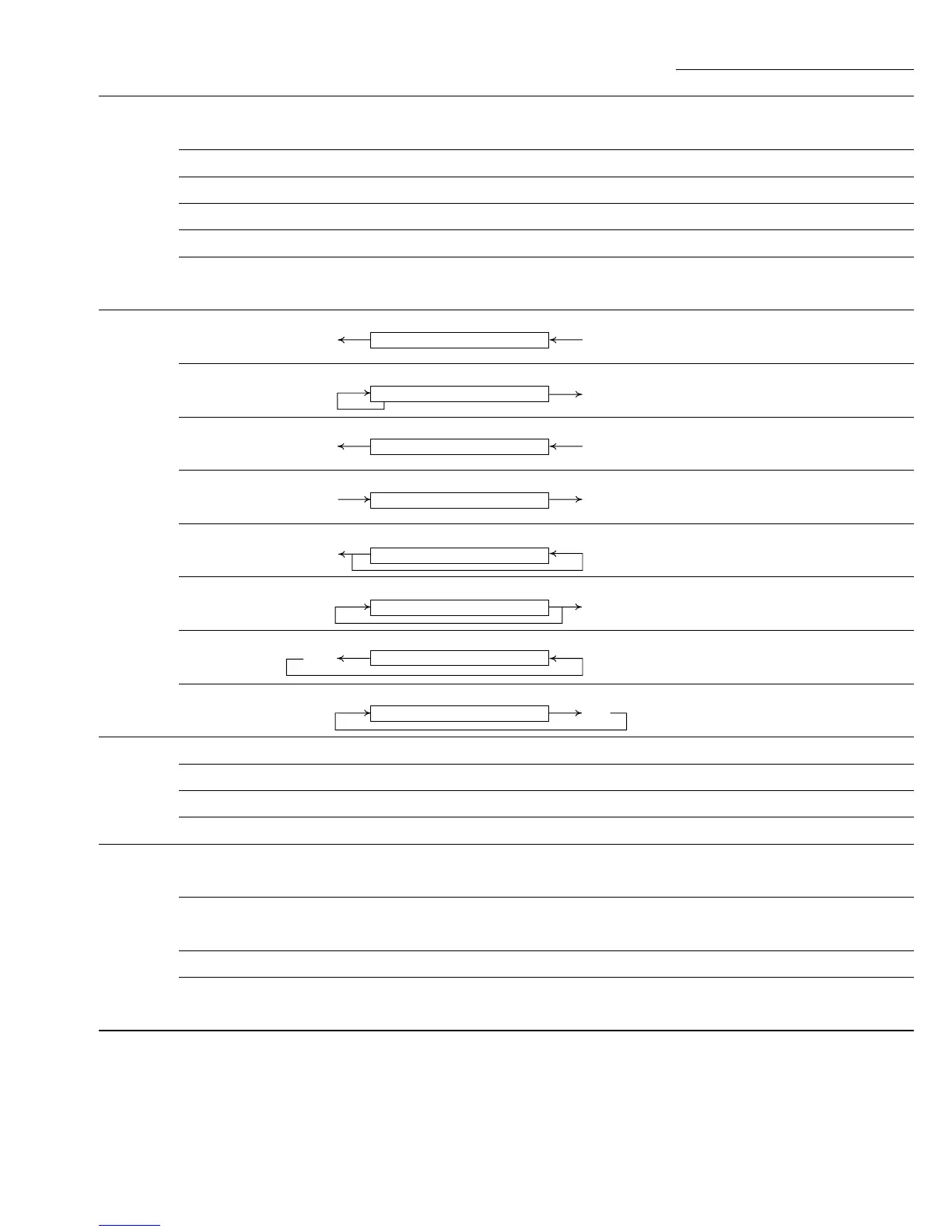

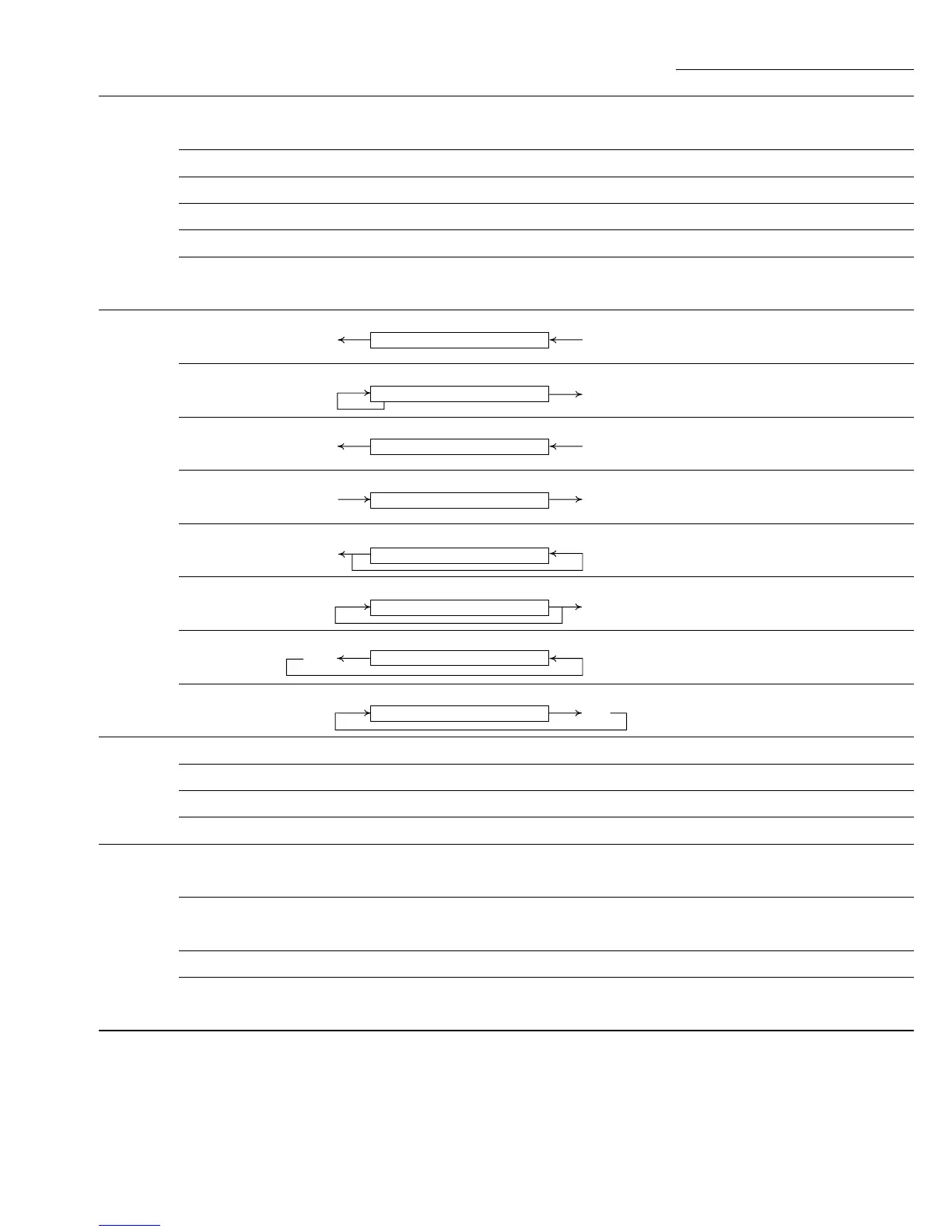

Shift SHAL B/W ↕↕↕↕

opera-

tions SHAR B/W ↕↕0 ↕

SHLL B/W ↕↕0 ↕

SHLR B/W 0 ↕ 0 ↕

ROTL B/W ↕↕0 ↕

ROTR B/W ↕↕0 ↕

ROTXL B/W ↕↕0 ↕

ROTXR B/W ↕↕0 ↕

Logic AND Rd ∧ (EAs) → Rd B/W ↕↕0—

opera- OR Rd ∨ (EAs) → Rd B/W ↕↕0—

tions XOR Rd ⊕ (EAs) → Rd B/W ↕↕0—

NOT ¬ (EAd) → (EAd) B/W ↕↕0—

Bit BSET ¬ (< Bit number > of < EAd >) → Z B/W — ↕ ——

manipu- 1 → (< Bit number > of < EAd >)

lations BCLR ¬ (< Bit number > of < EAd >) → Z B/W — ↕ ——

0 → (< Bit number > of < EAd >)

BTST ¬ (< Bit number > of < EAd >) → Z B/W — ↕ ——

BNOT ¬ (< Bit number > of < EAd >) → Z B/W — ↕ ——

→ (< Bit number > of < EAd >)

MSB LSB

MSB LSB

MSB LSB

MSB LSB

MSB LSB

MSB LSB

MSB LSB

MSB LSB

C

C

C

C

0

C

C

0

0

C

C

339

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...