391

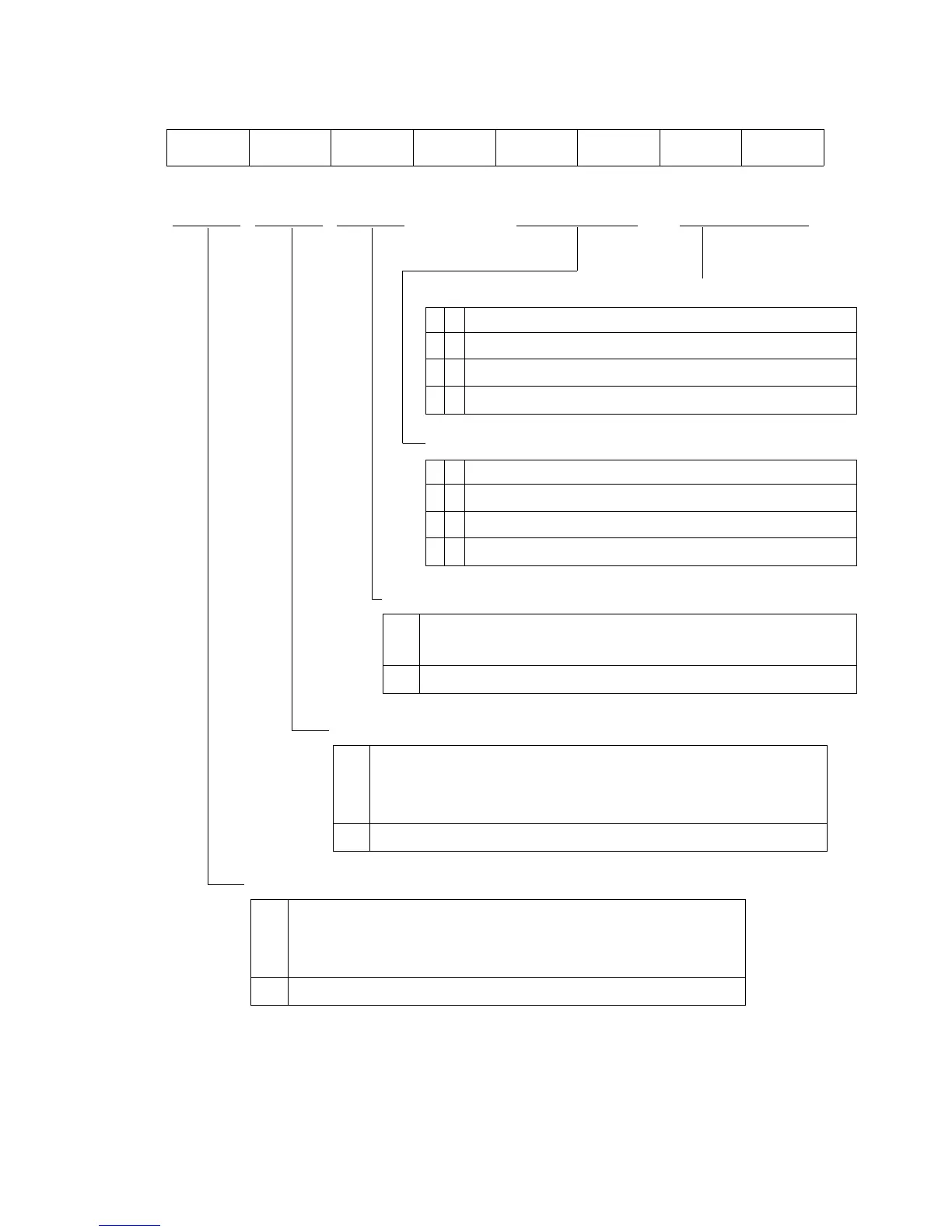

TCSR—Timer Control/Status Register H'FFD1 TMR

Bit 76543210

CMFB CMFA OVF — OS3

*

2

OS2

*

2

OS1

*

2

OS0

*

2

Initial value 00010000

Read/Write R/(W)

*

1

R/(W)

*

1

R/(W)

*

1

— R/W R/W R/W R/W

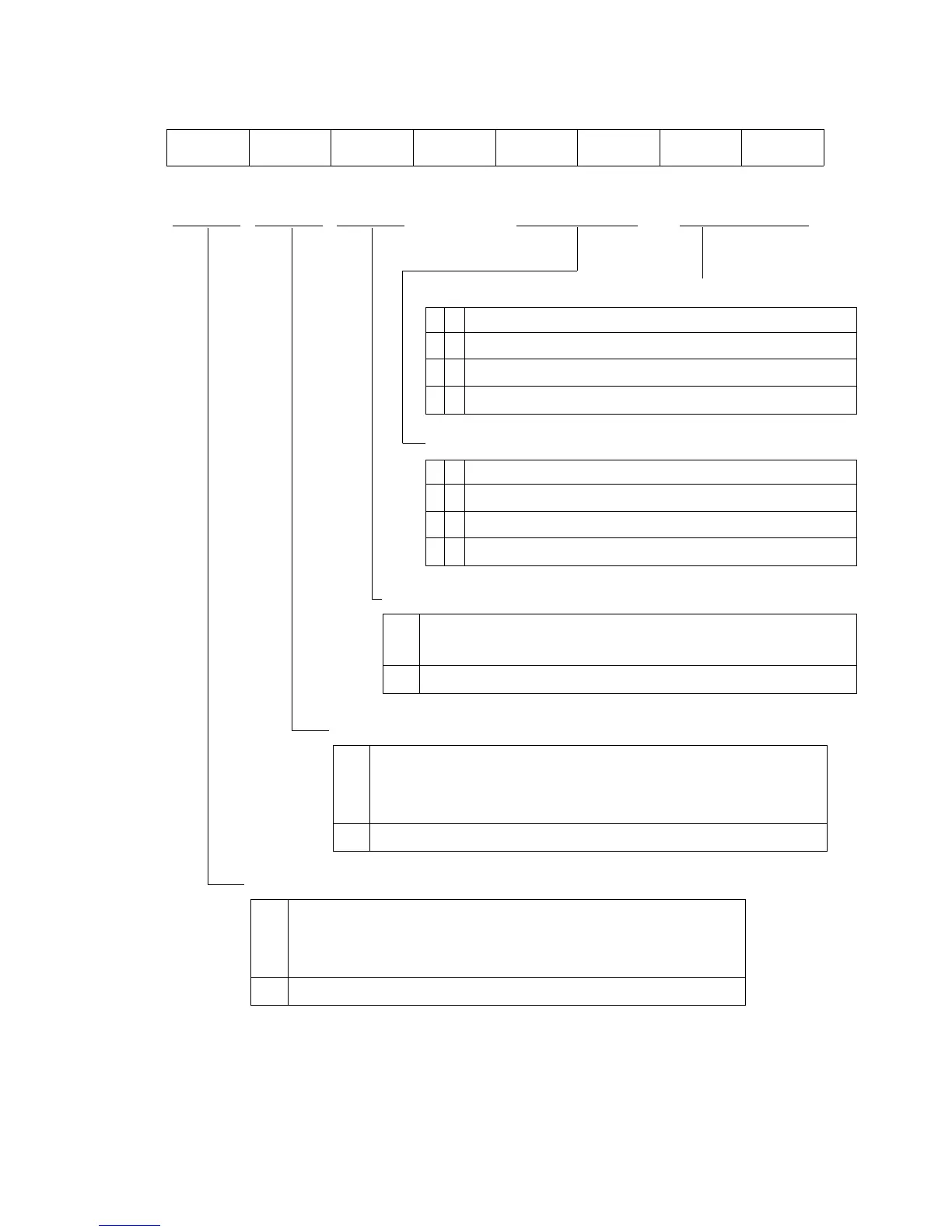

Output Select

0 0 No change on compare-match B.

0 1 Output 0 on compare-match B.

1 0 Output 1 on compare-match B.

1 1 Invert (toggle) output on compare-match B.

Output Select

0 0 No change on compare-match A.

0 1 Output 0 on compare-match A.

1 0 Output 1 on compare-match A.

1 1 Invert (toggle) output on compare-match A.

Timer Overflow Flag

0 Cleared from 1 to 0 when CPU reads OVF =

1, then writes 0 in OVF.

1 Set to 1 when TCNT changes from H'FF to H'00.

Compare-Match Flag B

0 Cleared from 1 to 0 when:

1. CPU reads CMFB = 1, then writes 0 in CMFB.

2. CMB interrupt is served by the DTC.

1 Set to 1 when TCNT = TCORB.

*1 Only writing of 0 to clear the flag is enabled.

*2 When all four bits (OS3 to OS0) are cleared to 0, output is disabled.

Compare-Match Flag A

0 Cleared from 1 to 0 when:

1. CPU reads CMFA = 1, then writes 0 in CMFA.

2. CMA interrupt is served by the DTC.

1 Set to 1 when TCNT = TCORA.

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...