7.3 Operation

7.3.6 Management to Resume Slave CPU Synchronization

7-24

7.3.6 Management to Resume Slave CPU Synchronization

The slave CPU synchronous process is automatically carried out when its execution requirements are met.

Here, in a transient state from slave CPU asynchronous to slave CPU synchronous state, the following operations are

carried out by the system:

• Start of timing adjustment of the slave scan cycle

• When SVB-01 is attached to a optional slave slot, the MECHATROLINK communication is reset

As a result operation of the slave side application is affected as follows:

• One scan with a longer cycle than the setup time occurs

• When a servo connected to the SVB-01 is running, its axis stops and an alarm occurs

To avoid these impacts (to avoid automatic recovery to the slave CPU synchronous state), use the slave side application

to operate a control bit “SLVSC (slave CPU synchronous resume control)”.

Operating this bit allows you to control the synchronous process.

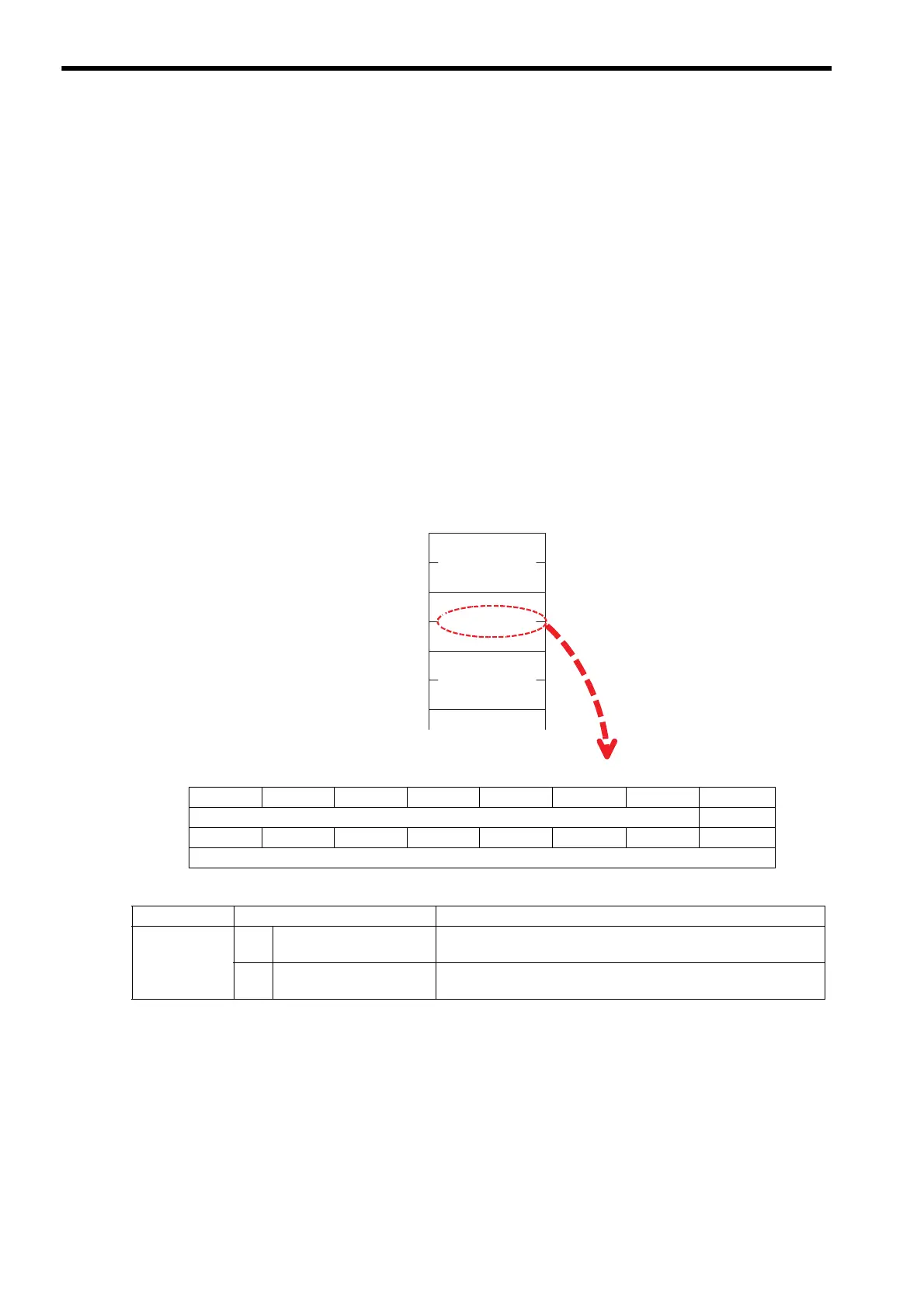

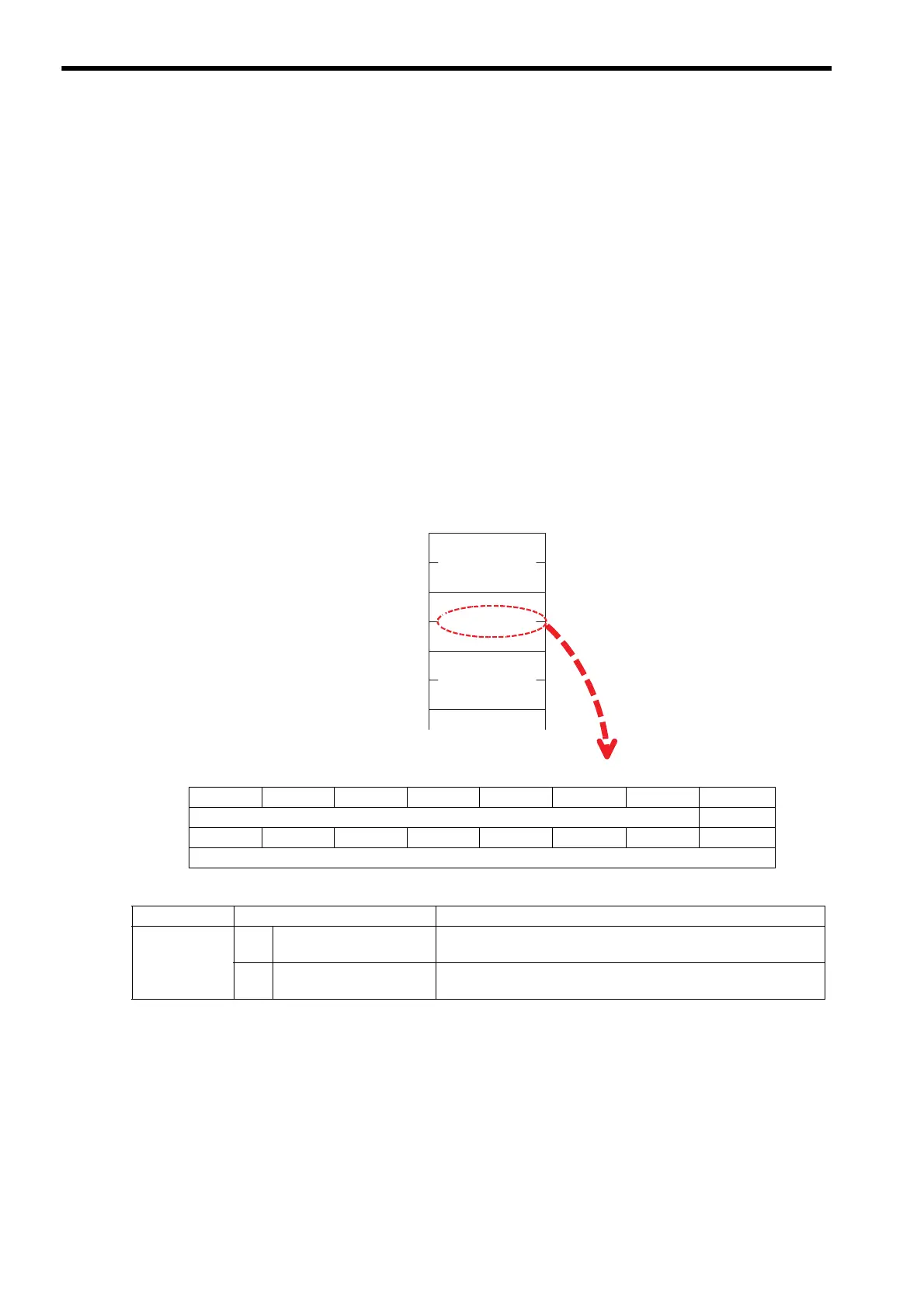

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Unused SLVSC

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

Unused

Name Definition Description

SLVSC

0

Resume enable

When out of slave CPU synchronization, the slave CPU synchroniza-

tion is automatically resumed.

1

Resume disable

Even when out of slave CPU synchronization, the operation continues

in an asynchronous state.

High

Low

OWxxxx+0

OWxxxx+1

OWxxxx+2

7 6 5 4 3 2 1 0

MP2300S (slave)

[Output register]

Scan counter

unused

Control bit

Data 1

Loading...

Loading...