GR712RC-UM, Jun 2017, Version 2.9 139 www.cobham.com/gaisler

GR712RC

18.4.4 Status register

The status register is read only and reflects the current status of the core.

Receive buffer status is cleared when the Release receive buffer command is given and set high if

there are more messages available in the fifo.

The data overrun status signals that a message which was accepted could not be placed in the fifo

because not enough space left. NOTE: This bit differs from the SJA1000 behavior and is set first

when the fifo has been read out.

When the transmit buffer status is high the transmit buffer is available to be written into by the CPU.

During an on-going transmission the buffer is locked and this bit is 0.

The transmission complete bit is set to 0 when a transmission request has been issued and will not be

set to 1 again until a message has successfully been transmitted.

18.4.5 Interrupt register

The interrupt register signals to CPU what caused the interrupt. The interrupt bits are only set if the

corresponding interrupt enable bit is set in the control register.

This register is reset on read with the exception of IR.0. Note that this differs from the SJA1000

behavior where all bits are reset on read in BasicCAN mode. This core resets the receive interrupt bit

when the release receive buffer command is given (like in PeliCAN mode).

Also note that bit IR.5 through IR.7 reads as 1 but IR.4 is 0.

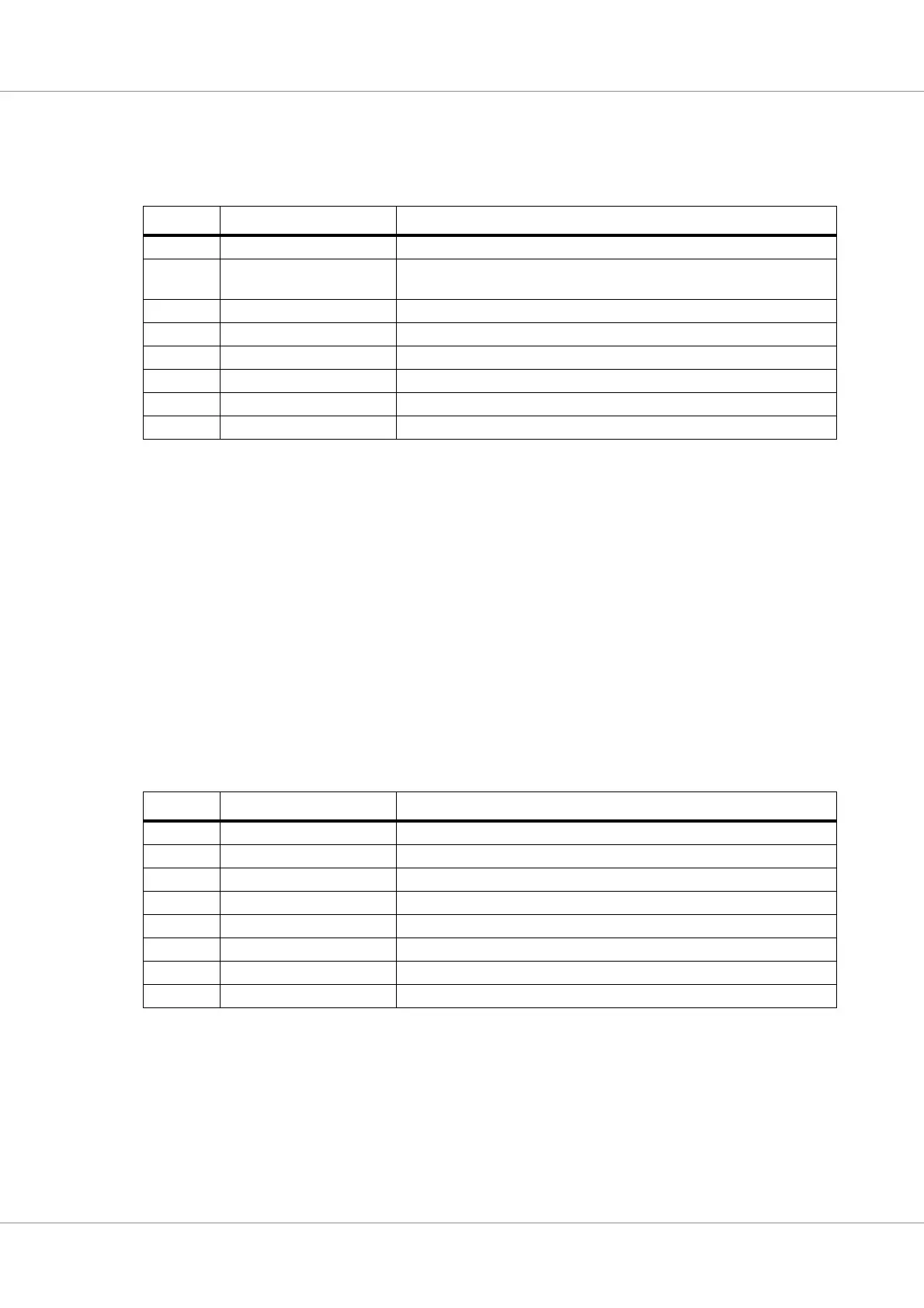

Table 124.Bit interpretation of status register (SR) (address 2)

Bit Name Description

SR.7 Bus status 1 when the core is in bus-off and not involved in bus activities

SR.6 Error status At least one of the error counters have reached or exceeded the CPU warning

limit (96).

SR.5 Transmit status 1 when transmitting a message

SR.4 Receive status 1 when receiving a message

SR.3 Transmission complete 1 indicates the last message was successfully transferred.

SR.2 Transmit buffer status 1 means CPU can write into the transmit buffer

SR.1 Data overrun status 1 if a message was lost because no space in fifo.

SR.0 Receive buffer status 1 if messages available in the receive fifo.

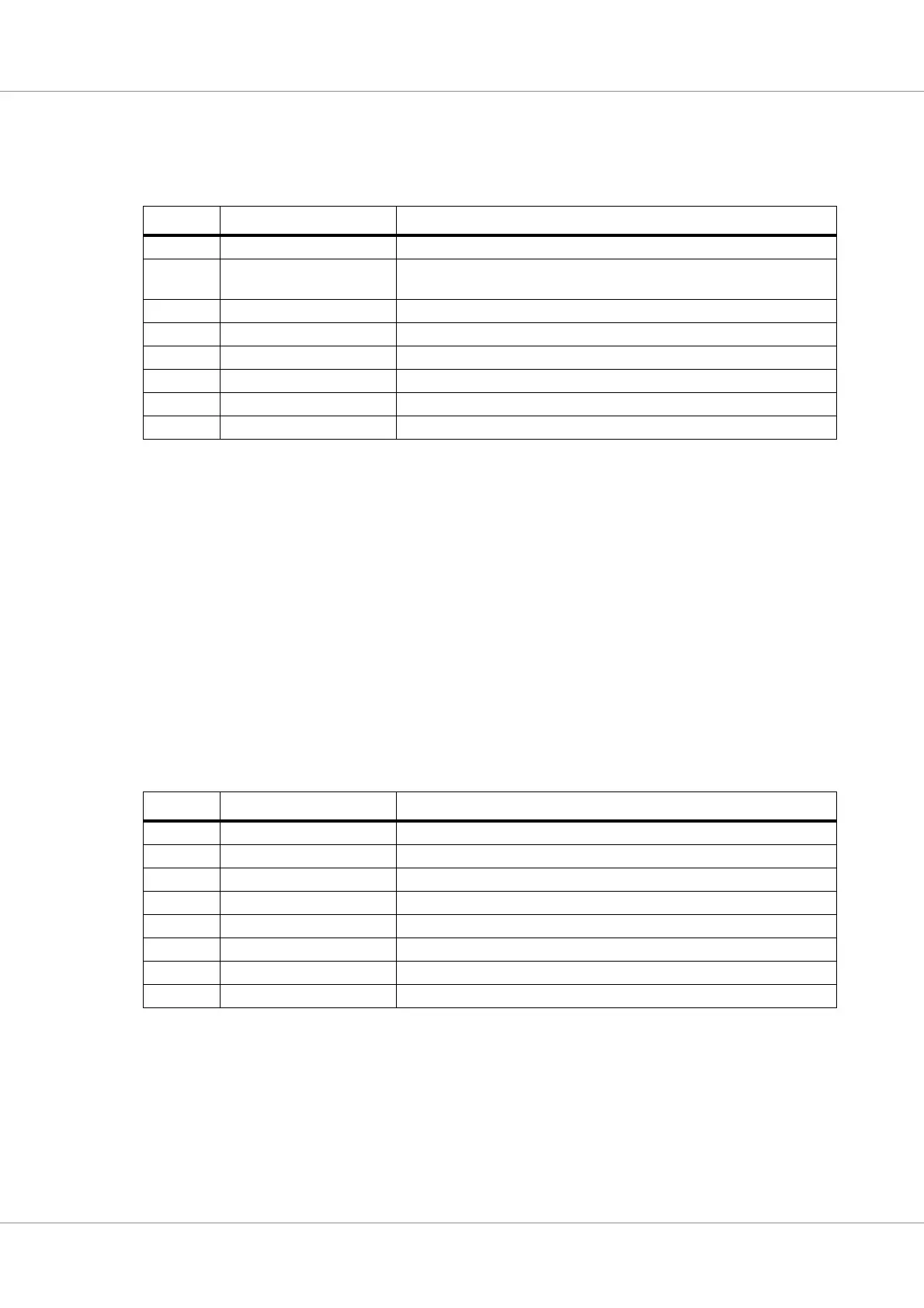

Table 125.Bit interpretation of interrupt register (IR) (address 3)

Bit Name Description

IR.7 - reserved

IR.6 - reserved

IR.5 - reserved

IR.4 - not used (wake-up interrupt of SJA1000)

IR.3 Data overrun interrupt Set when SR.1 goes from 0 to 1.

IR.2 Error interrupt Set when the error status or bus status are changed.

IR.1 Transmit interrupt Set when the transmit buffer is released (status bit 0->1)

IR.0 Receive interrupt This bit is set while there are more messages in the fifo.

Loading...

Loading...