GR712RC-UM, Jun 2017, Version 2.9 145 www.cobham.com/gaisler

GR712RC

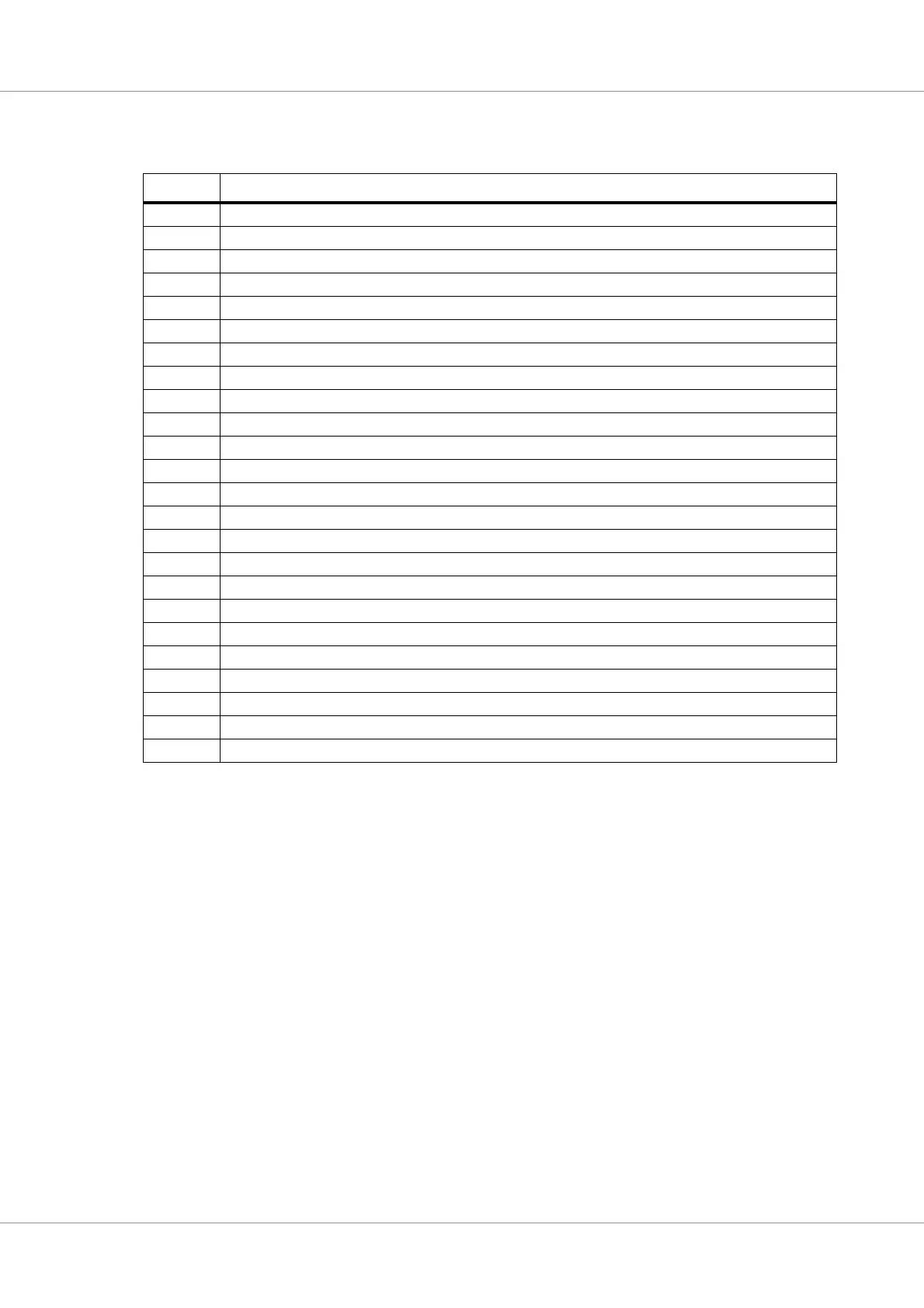

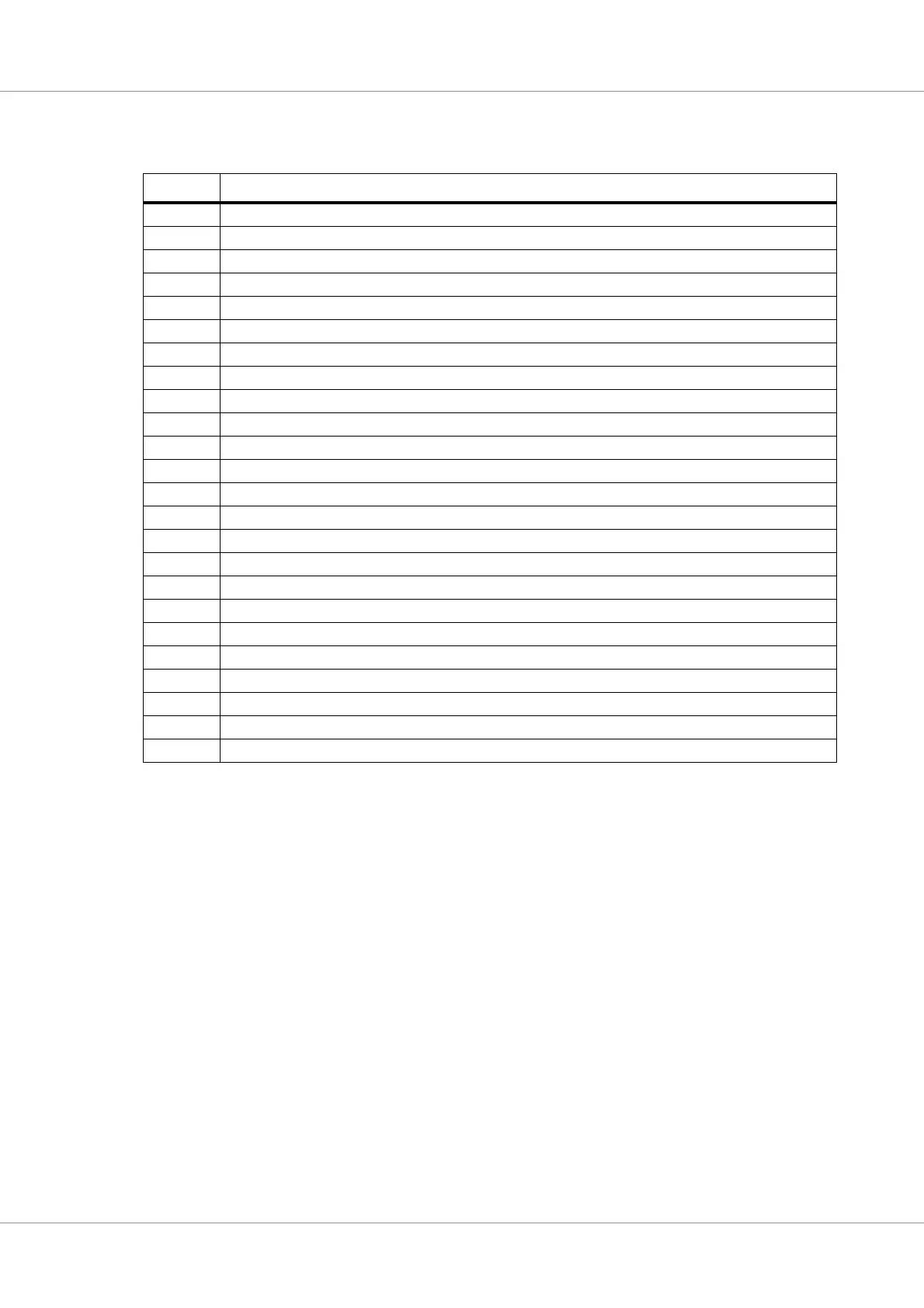

Bit 4 downto 0 of the ECC register is interpreted as below

18.5.9 Error warning limit register

This registers allows for setting the CPU error warning limit. It defaults to 96. Note that this register is

only writable in reset mode.

18.5.10 RX error counter register (address 14)

This register shows the value of the rx error counter. It is writable in reset mode. A bus-off event

resets this counter to 0.

18.5.11 TX error counter register (address 15)

This register shows the value of the tx error counter. It is writable in reset mode. If a bus-off event

occurs this register is initialized as to count down the protocol defined 128 occurrences of the bus-free

signal and the status of the bus-off recovery can be read out from this register. The CPU can force a

bus-off by writing 255 to this register. Note that unlike the SJA1000 this core will signal bus-off

immediately and not first when entering operating mode. The bus-off recovery sequence starts when

entering operating mode after writing 255 to this register in reset mode.

Table 136.Bit interpretation of ECC.4-0

ECC.4-0 Description

0x03 Start of frame

0x02 ID.28 - ID.21

0x06 ID.20 - ID.18

0x04 Bit SRTR

0x05 Bit IDE

0x07 ID.17 - ID.13

0x0F ID.12 - ID.5

0x0E ID.4 - ID.0

0x0C Bit RTR

0x0D Reserved bit 1

0x09 Reserved bit 0

0x0B Data length code

0x0A Data field

0x08 CRC sequence

0x18 CRC delimiter

0x19 Acknowledge slot

0x1B Acknowledge delimiter

0x1A End of frame

0x12 Intermission

0x11 Active error flag

0x16 Passive error flag

0x13 Tolerate dominant bits

0x17 Error delimiter

0x1C Overload flag

Loading...

Loading...