GR712RC-UM, Jun 2017, Version 2.9 144 www.cobham.com/gaisler

GR712RC

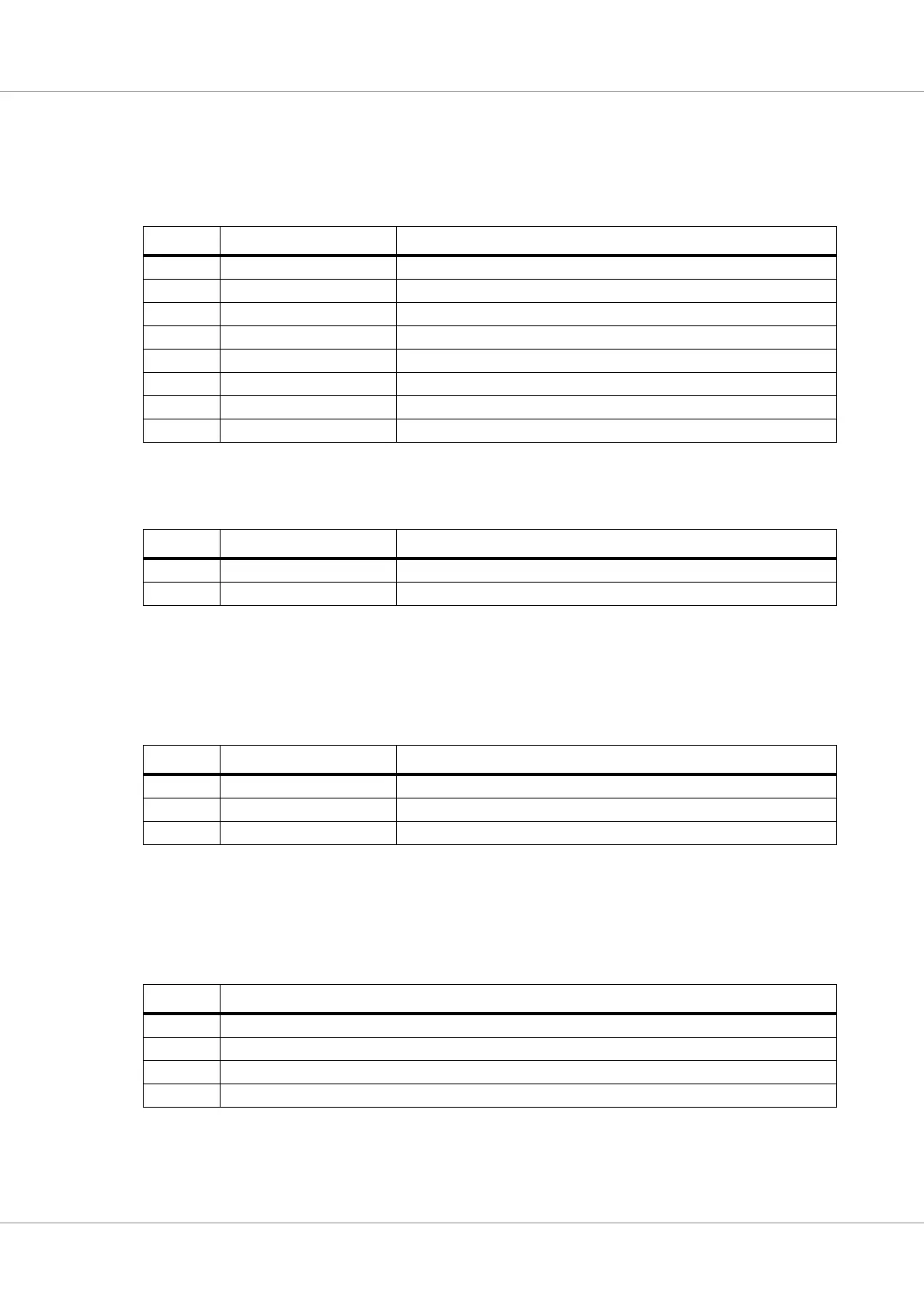

18.5.6 Interrupt enable register

In the interrupt enable register the separate interrupt sources can be enabled/disabled. If enabled the

corresponding bit in the interrupt register can be set and an interrupt generated.

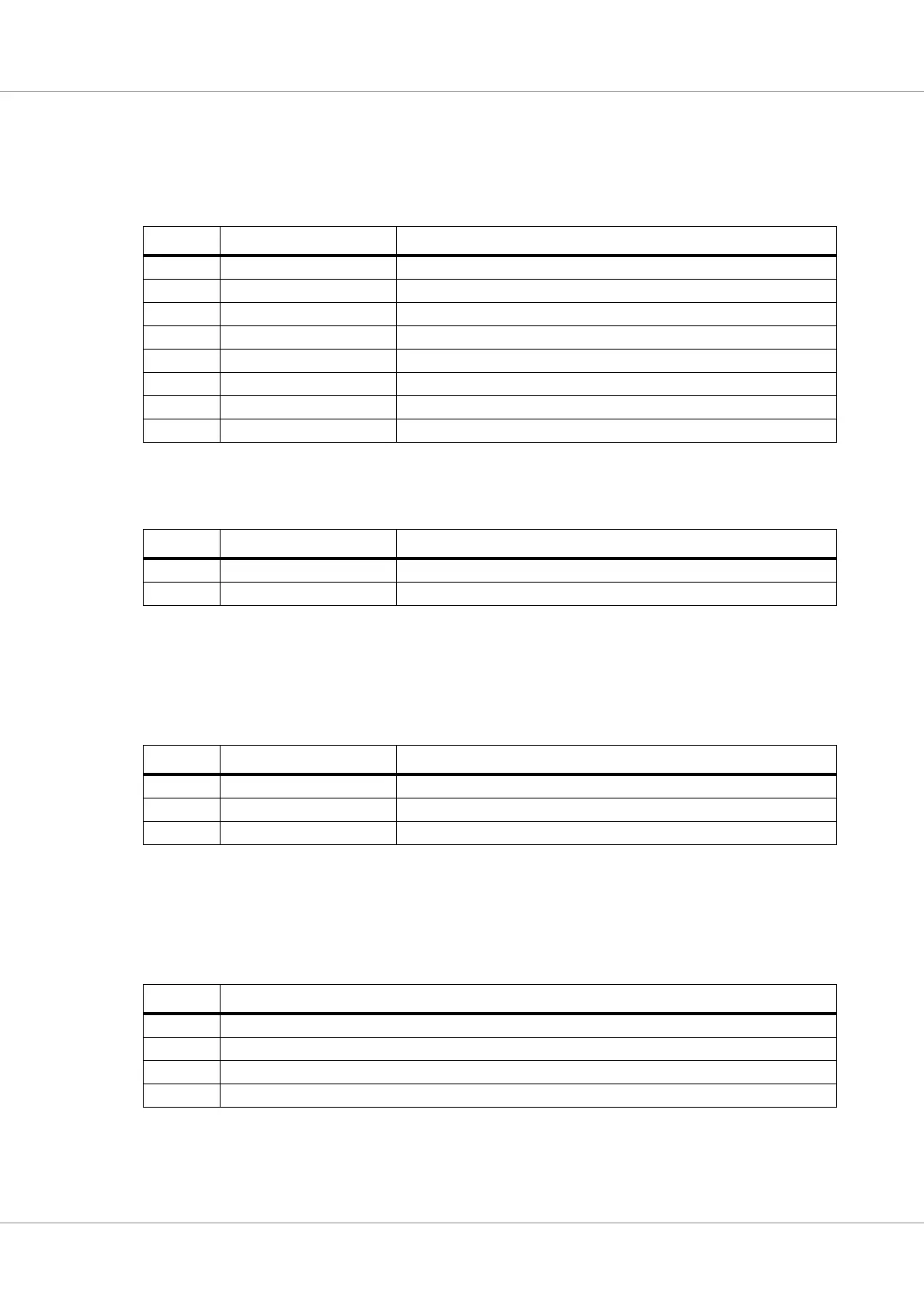

18.5.7 Arbitration lost capture register

Table 133.Bit interpretation of arbitration lost capture register (ALC) (address 11)

When the core loses arbitration the bit position of the bit stream processor is captured into arbitration

lost capture register. The register will not change content again until read out.

18.5.8 Error code capture register

Table 134.Bit interpretation of error code capture register (ECC) (address 12)

When a bus error occurs the error code capture register is set according to what kind of error occurred,

if it was while transmitting or receiving and where in the frame it happened. As with the ALC register

the ECC register will not change value until it has been read out. The table below shows how to inter-

pret bit 7-6 of ECC.

Table 132.Bit interpretation of interrupt enable register (IER) (address 4)

Bit Name Description

IR.7 Bus error interrupt 1 - enabled, 0 - disabled

IR.6 Arbitration lost interrupt 1 - enabled, 0 - disabled

IR.5 Error passive interrupt 1 - enabled, 0 - disabled

IR.4 - not used (wake-up interrupt of SJA1000)

IR.3 Data overrun interrupt 1 - enabled, 0 - disabled

IR.2 Error warning interrupt 1 - enabled, 0 - disabled.

IR.1 Transmit interrupt 1 - enabled, 0 - disabled

IR.0 Receive interrupt 1 - enabled, 0 - disabled

Bit Name Description

ALC.7-5

- reserved

ALC.4-0 Bit number Bit where arbitration is lost

Bit Name Description

ECC.7-6

Error code Error code number

ECC.5 Direction 1 - Reception, 0 - transmission error

ECC.4-0 Segment Where in the frame the error occurred

Table 135.Error code interpretation

ECC.7-6 Description

0 Bit error

1 Form error

2Stuff error

3Other

Loading...

Loading...