GR712RC-UM, Jun 2017, Version 2.9 47 www.cobham.com/gaisler

GR712RC

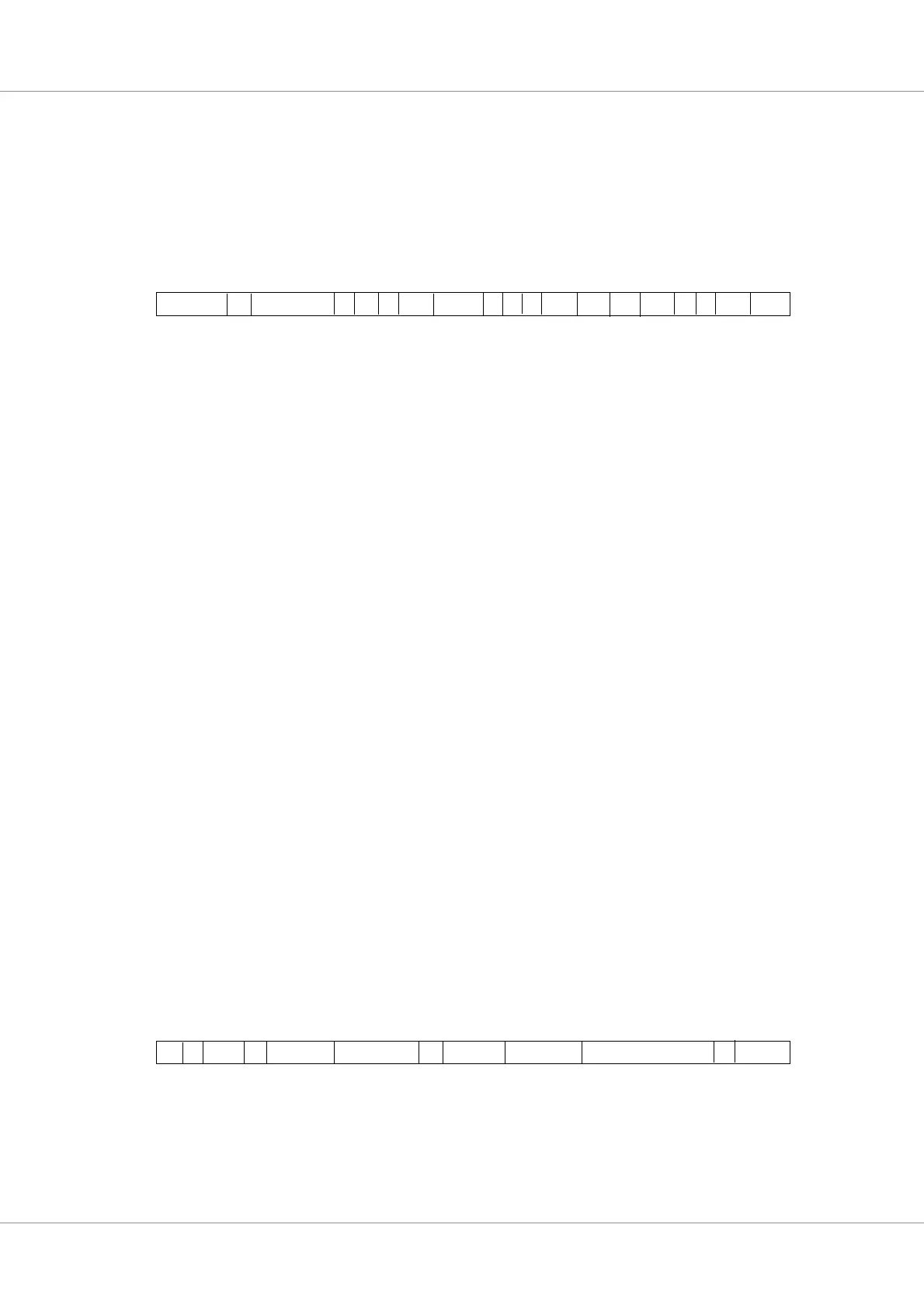

4.5.4 Cache Control Register

The operation of the instruction and data caches is controlled through a common Cache Control Reg-

ister (CCR) (figure 8). Each cache can be in one of three modes: disabled, enabled and frozen. If dis-

abled, no cache operation is performed and load and store requests are passed directly to the memory

controller. If enabled, the cache operates as described above. In the frozen state, the cache is accessed

and kept in sync with the main memory as if it was enabled, but no new lines are allocated on read

misses.

[28]: Parity Select [PS] - if set diagnostic read will return 4 check bits in the lsb bits, otherwise tag or data word is

returned.

[27:24]: Test Bits [TB] - if set, check bits will be xored with test bits TB during diagnostic write

[23]: Data cache snoop enable [DS] - if set, will enable data cache snooping.

[22]: Flush data cache (FD). If set, will flush the data cache. Always reads as zero.

[21]: Flush Instruction cache (FI). If set, will flush the instruction cache. Always reads as zero.

[20:19]: FT scheme: “00” = no FT, “01” = 4-bit checking implemented

[16]: Instruction burst fetch (IB). This bit enables burst fill during instruction fetch.

[15]: Instruction cache flush pending (IP). This bit is set when an instruction cache flush operation is in progress.

[14]: Data cache flush pending (DP). This bit is set when an data cache flush operation is in progress.

[13:12]: Instruction Tag Errors (ITE) - Number of detected parity errors in the instruction tag cache.

[11:10]: Instruction Data Errors (IDE) - Number of detected parity errors in the instruction data cache.

[9:8]: Data Tag Errors (DTE) - Number of detected parity errors in the data tag cache.

[7:6]: Data Data Errors (IDE) - Number of detected parity errors in the data data cache.

[5]: Data Cache Freeze on Interrupt (DF) - If set, the data cache will automatically be frozen when an asynchronous

interrupt is taken.

[4]: Instruction Cache Freeze on Interrupt (IF) - If set, the instruction cache will automatically be frozen when an

asynchronous interrupt is taken.

[3:2]: Data Cache state (DCS) - Indicates the current data cache state according to the following: X0= disabled, 01 =

frozen, 11 = enabled.

[1:0]: Instruction Cache state (ICS) - Indicates the current data cache state according to the following: X0= disabled, 01

= frozen, 11 = enabled.

If the DF or IF bit is set, the corresponding cache will be frozen when an asynchronous interrupt is

taken. This can be beneficial in real-time system to allow a more accurate calculation of worst-case

execution time for a code segment. The execution of the interrupt handler will not evict any cache

lines and when control is returned to the interrupted task, the cache state is identical to what it was

before the interrupt. If a cache has been frozen by an interrupt, it can only be enabled again by

enabling it in the CCR. This is typically done at the end of the interrupt handler before control is

returned to the interrupted task.

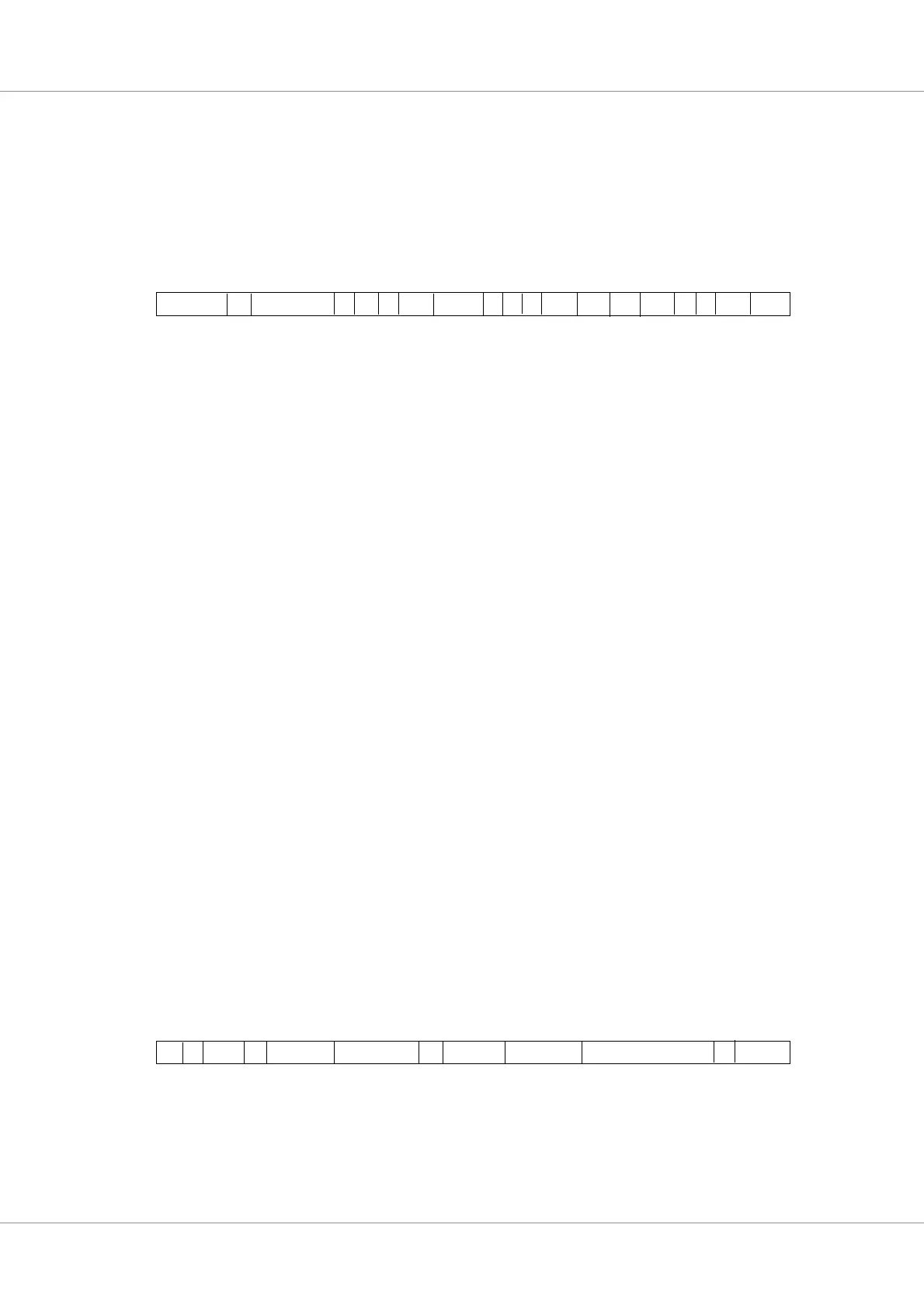

4.5.5 Cache configuration registers

The configuration of the two caches if defined in two registers: the instruction and data configuration

registers. These registers are read-only and indicate the size and configuration of the caches.

[31]: Cache locking (CL). Set if cache locking is implemented.

[29:28]: Cache replacement policy (REPL). 00 - no replacement policy (direct-mapped cache), 01 - least recently used

(LRU), 10 - least recently replaced (LRR), 11 - random

[27]: Cache snooping (SN). Set if snooping is implemented.

Figure 8. Cache control register

ICSDCSIF

IB

0123

4

514

15

1631

DPIP

DF

6

21

FI

FD

2223

DS

7

DDE

DTEIDEITE

8910111213

27

28

TBPS

29

24

20 19

FT

Figure 9. Cache configuration register

SETS LRSTART

03

4

18 12

15

1631 1119

LSIZE

LR

2023

SSIZE

SN

REPLCL

30 29

28

27 26 25 24

LRSIZE

M

Loading...

Loading...