GR712RC-UM, Jun 2017, Version 2.9 67 www.cobham.com/gaisler

GR712RC

5.14.1 Memory configuration register 1 (MCFG1)

Memory configuration register 1 is used to program the timing of rom and IO accesses.

During reset, the MSB PROM width bit (MCFG1[9]) is set to the value of SWMX[6], while the LSB

bit (MCFG1[8]) is set to 0. The prom waitstates fields are set to 15 (maximum). External bus error

and bus ready are disabled. All other fields are undefined.

5.14.2 Memory configuration register 2 (MCFG2)

Memory configuration register 2 is used to control the timing of the SRAM and SDRAM.

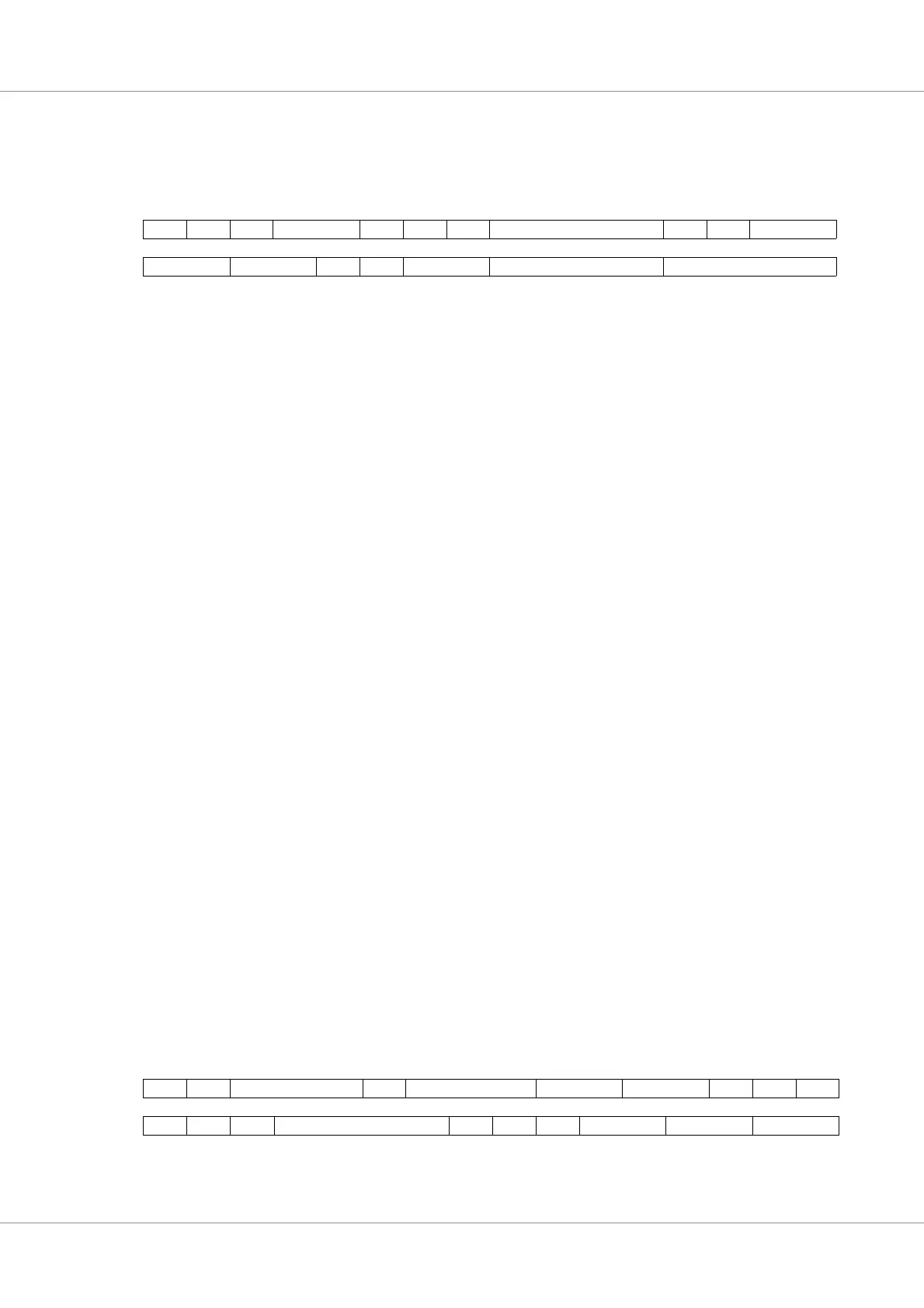

Table 29. Memory configuration register 1

31 30 29 28 27 26 25 24 23 20 19 18 17

PBRDY ABRDY IOBUSW IBRDY BEXCN IO WAITSTATES IOEN ROMBANKSZ

14 13 12 11 10 9 8 7 4 3 0

RESERVED PWEN PROM WIDTH PROM WRITE WS PROM READ WS

31 RESERVED

30 PROM area bus ready enable (PBRDY) - Enables bus ready (BRDYN) signalling for the PROM

area. Reset to ‘0’.

29 Asynchronous bus ready (ABRDY) - Enables asynchronous bus ready.

28: 27 I/O bus width (IOBUSW) - Sets the data width of the I/O area (“00”=8, “10” =32).

26 I/O bus ready enable (IBRDY) - Enables bus ready (BRDYN) signalling for the I/O area. Reset to

‘0’.

25 Bus error enable (BEXCN) - Enables bus error signalling for all areas. Reset to ‘0’.

24 RESERVED

23: 20 I/O waitstates (IO WAITSTATES) - Sets the number of waitstates during I/O accesses (“0000”=0,

“0001”=1, “0010”=2,..., “1111”=15).

19 I/O enable (IOEN) - Enables accesses to the memory bus I/O area.

18 RESERVED

17: 14 PROM bank size (ROMBANKSZ) - Returns current PROM bank size when read. “0000” is a spe-

cial case and corresponds to a bank size of 256 MiB. All other values give the bank size in binary

steps: “0001”=16KiB, “0010”=32KiB, “0011”=64KiB,... , “1011”=16 MiB (i.e. 8 KiB * 2**ROM-

BANKSZ).

For any value, two ROM chip select signals are available.

Programmable bank sizes can be changed by writing to this register field. The written values corre-

spond to the bank sizes and number of chip-selects as above. Reset to "0000".

13:12 RESERVED

11 PROM write enable (PWEN) - Enables write cycles to the PROM area.

10 RESERVED

9: 8 PROM width (PROM WIDTH) - Sets the data width of the PROM area (“00”=8, “10”=32).

7: 4 PROM write waitstates (PROM WRITE WS) - Sets the number of wait states for PROM write

cycles (“0000”=0, “0001”=2, “0010”=4,..., “1111”=30).

3: 0 PROM read waitstates (PROM READ WS) - Sets the number of wait states for PROM read cycles

(“0000”=0, “0001”=2, “0010”=4,...,”1111”=30). Reset to “1111”.

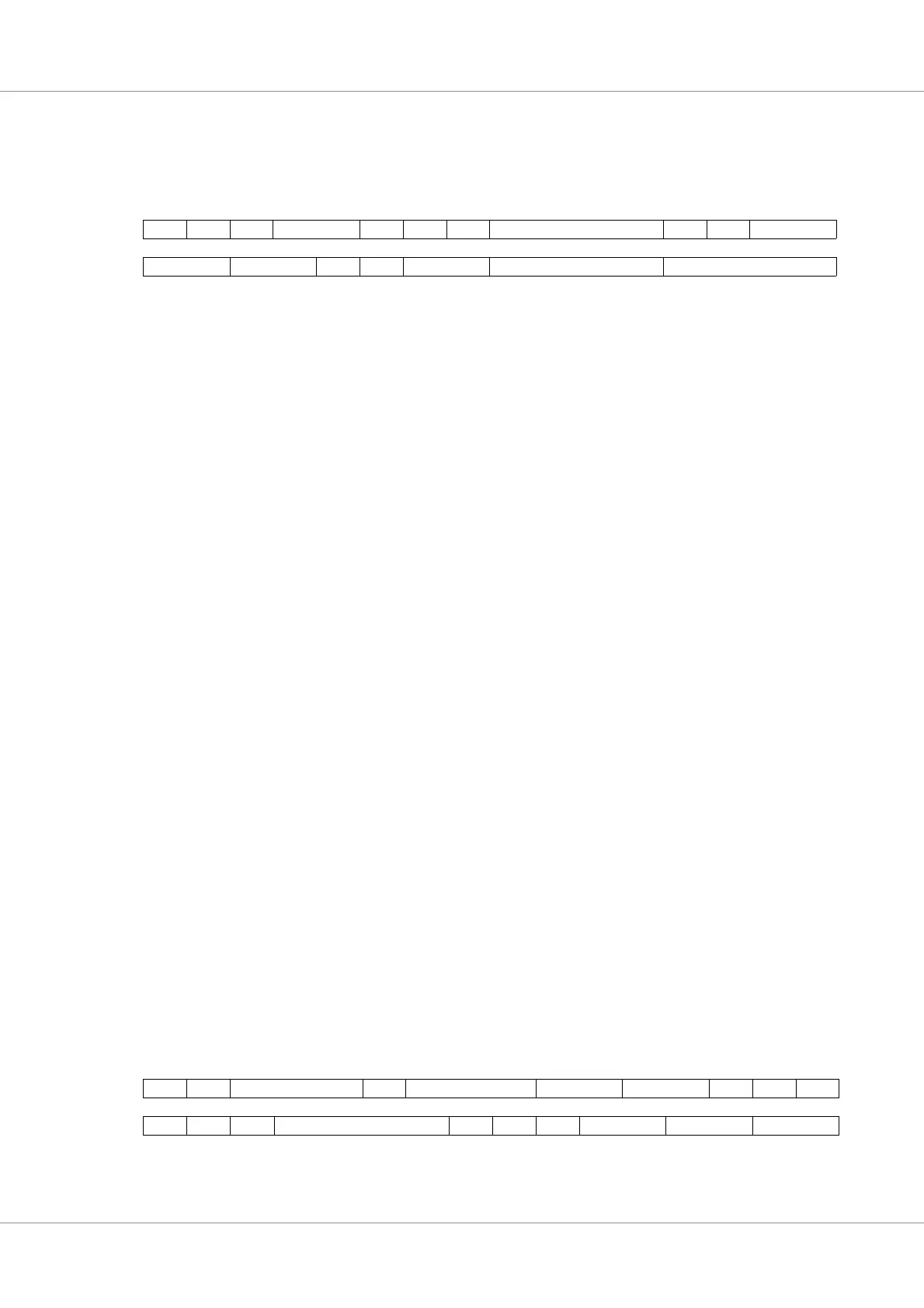

Table 30. Memory configuration register 2

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

SDRF TRP SDRAM TRFC TCAS SDRAM BANKSZ SDRAM COLSZ SDRAM CMD D64 SDPB

15141312 9876543210

SE SI RAM BANK SIZE RBRDY RMW RAM WIDTH RAM WRITE WS RAM READ WS

31 SDRAM refresh (SDRF) - Enables SDRAM refresh.

30 SDRAM TRP parameter (TRP) - t

RP

will be equal to 2 or 3 system clocks (0/1).

Loading...

Loading...