2 CPU MODULE INSTRUCTION

2.1 Sequence Instruction

43

2

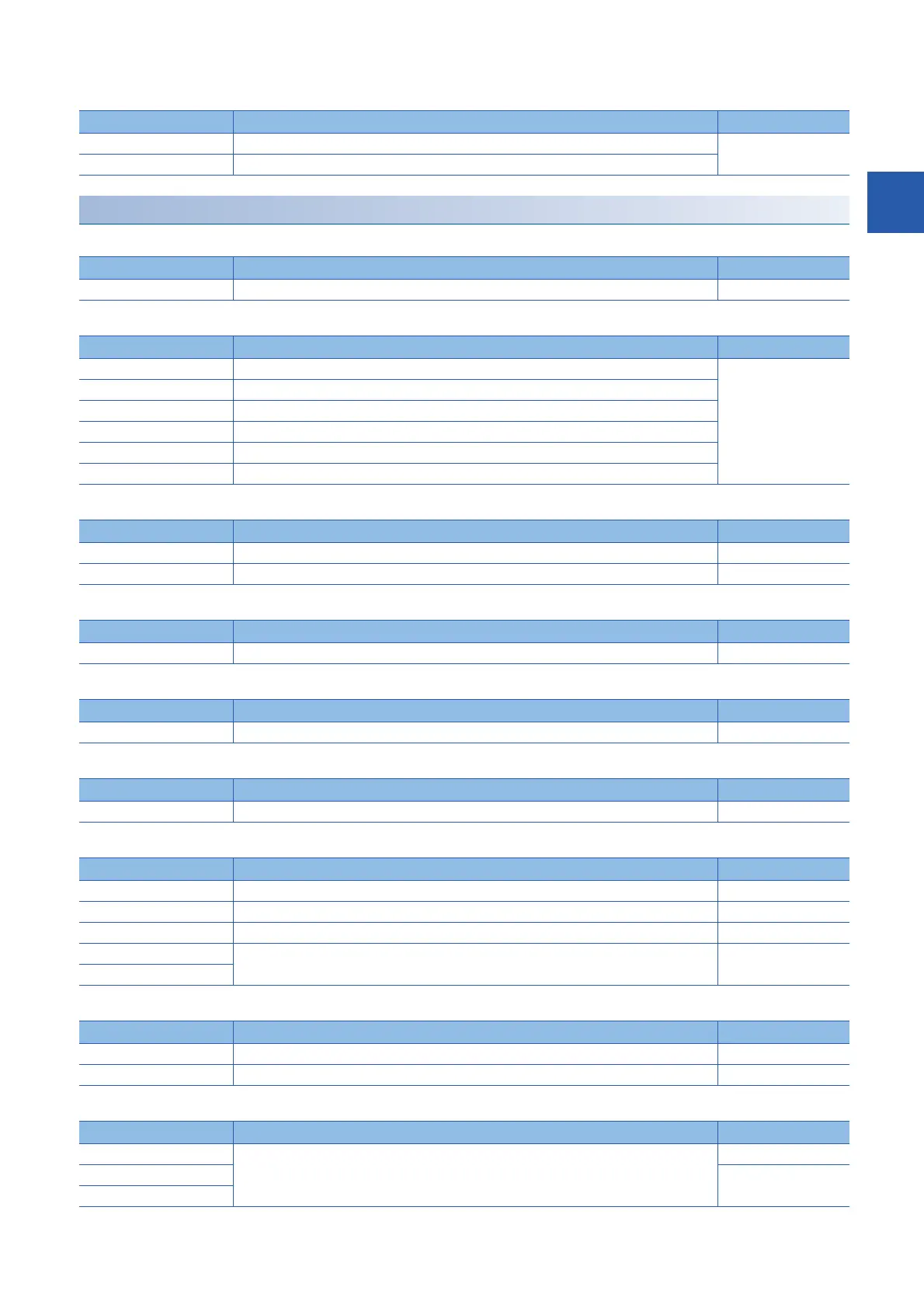

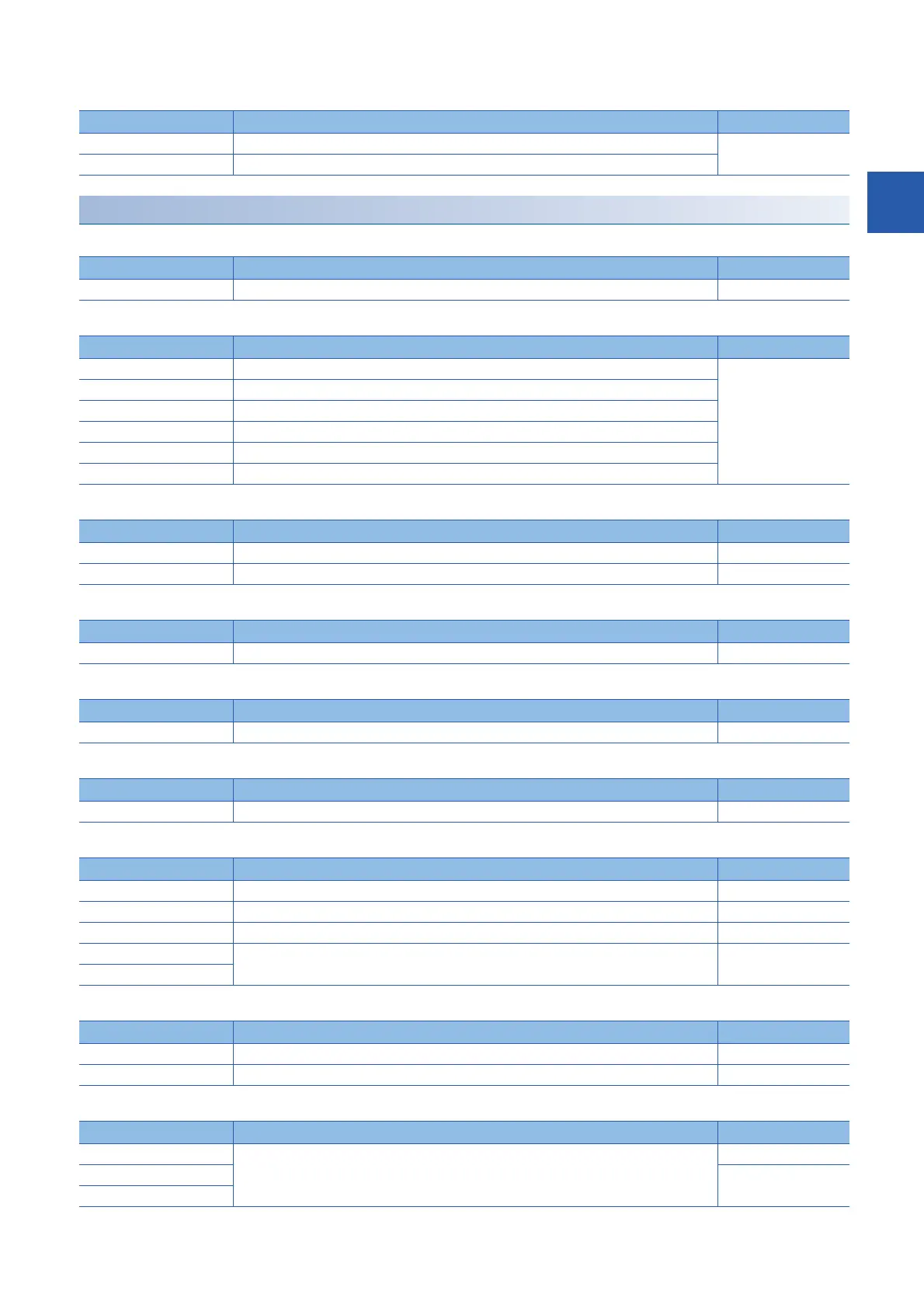

■Converting the operation result into a pulse

Output instruction

■Out (excluding the timer, counter and annunciator)

■Timer (low-speed, high-speed, low-speed retentive, high-speed retentive)

■Counter, long counter

■Annunciator

■Setting devices (excluding annunciator)

■Resetting devices (excluding annunciator)

■Setting/resetting annunciator

■Rising/falling edge output

■Inverting the bit device output

Instruction symbol Description Reference

MEP Conversion of operation result to rising edge pulse Page 107

MEF Conversion of operation result to falling edge pulse

Instruction symbol Description Reference

OUT Device output Page 108

Instruction symbol Description Reference

OUT T Low-speed timer Page 109

OUTH T Timer

OUTHS T High-speed timer

OUT ST Low-speed retentive timer

OUTH ST Retentive timer

OUTHS ST High-speed retentive timer

Instruction symbol Description Reference

OUT C Counter Page 111

OUT LC Long counter Page 112

Instruction symbol Description Reference

OUT F Annunciator Page 113

Instruction symbol Description Reference

SET Sets devices Page 114

Instruction symbol Description Reference

RST Resets devices Page 115

Instruction symbol Description Reference

SET F Sets annunciator Page 116

RST F Resets annunciator Page 117

ANS Sets annunciator (with evaluation time) Page 118

ANR Resets annunciator (smallest number reset) Page 119

ANRP

Instruction symbol Description Reference

PLS Generates a pulse for 1 cycle of a program at the rising edge of the input signal. Page 120

PLF Generates a pulse for 1 cycle of a program at the falling edge of the input signal. Page 122

Instruction symbol Description Reference

FF Inversion of device output Page 123

ALT Page 124

ALTP

Loading...

Loading...