2.2 Part Names

2-7

2

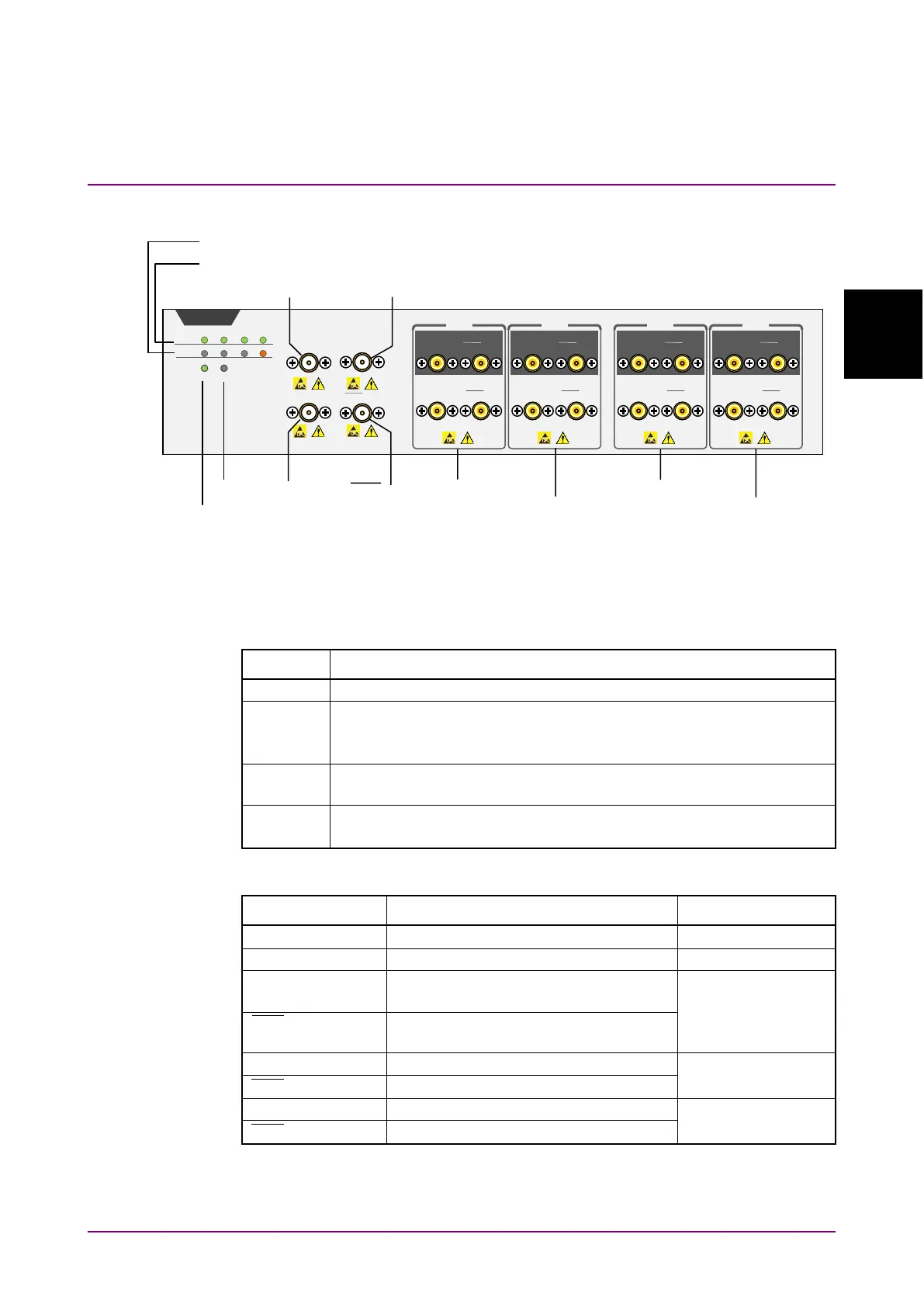

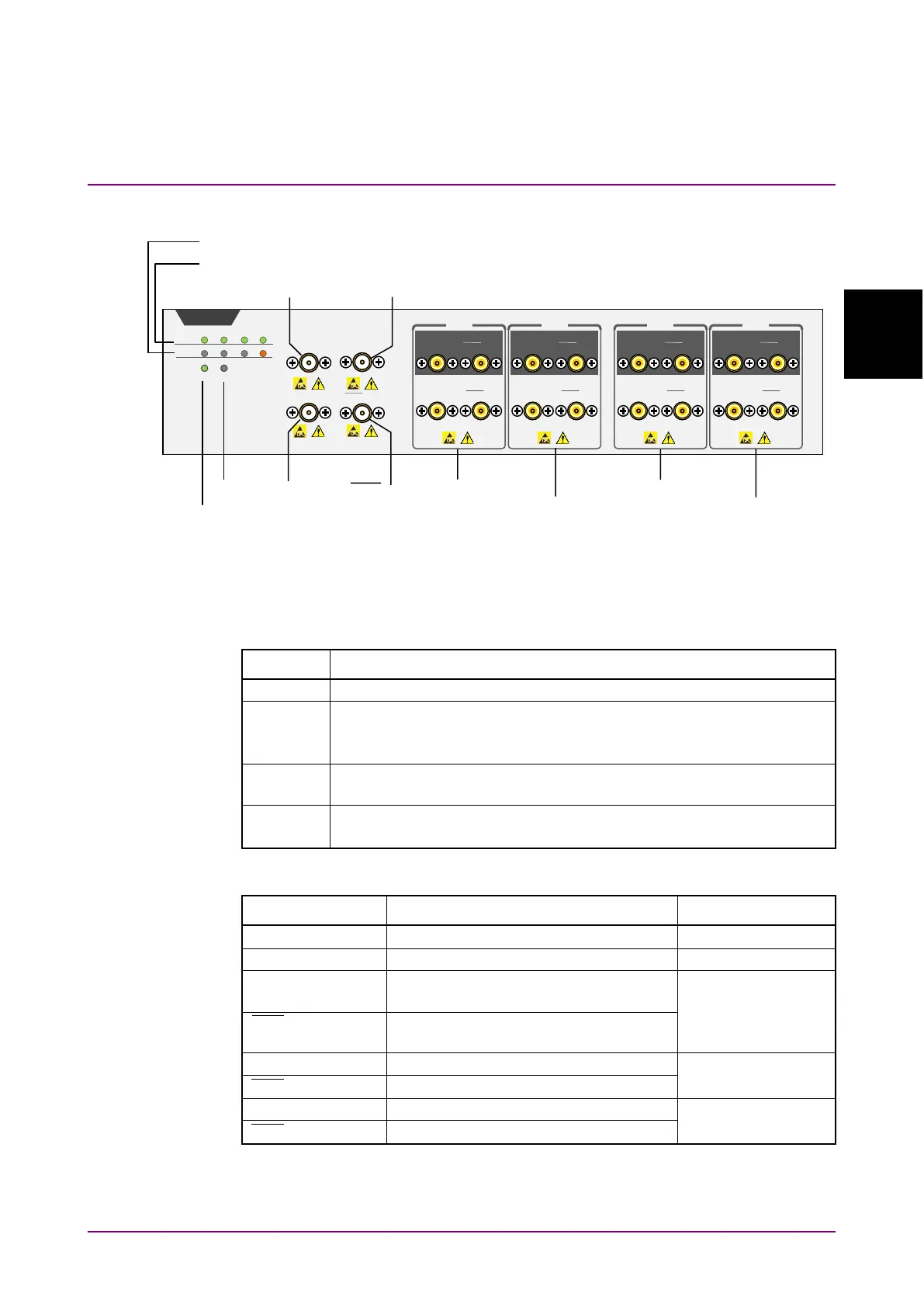

BERT Panel

Figure 2.2.1-3 BERT Panel Names (MP2110A-014)

The following tables describe the panel.

Table 2.2.1-2 Lamp List

Name Description

Lit green during signal output from PPG connector.

Lit orange at following condition at ED:

- Unable to synchronize pattern (Sync Loss).

Lit green during normal operation while able to receive remote

commands.

Lit red when hardware fault detected.

This may light briefly at power-on, but there is no abnormality.

Table 2.2.1-3 Connector List

Connector Name Description Level Range

For input of external clock.

Outputs the clock synchronized to

PPG pattern.

OH

Outputs the inverted clock

synchronized to PPG pattern.

OL

Outputs the PPG inverted data.

*: Same for Ch1 to Ch4.

Connectors

Connectors

1.6Vp-p Max

Loading...

Loading...