7.2 Performance Test for Error Detector

7-21

7

Performance Test

7.2.5 Error detection

(1) Specification

Error detection is possible under the following conditions:

Amplitude: 50 mV

Bit rate: 25.78125 Gbit/s

Pattern: PRBS31

Mark ratio: 50%

Single-end

Back-to-back connection

(2) Setup

Same as Figure 7.2.2-1 and Figure 7.2.2-2.

(3) Procedure

1. Connect the

Clk Out

connector and the

Trigger Clk In

connector

of the sampling oscilloscope using a coaxial cable.

2. Connect the coaxial terminators to the

ED1

Data

In

connector,

and

PPG1

Data

Out

connector.

3. Attach a 20 dB fixed attenuator to the

PPG1 Data Out

connector.

(Refer to (a) in Figure 7.2.2-1.)

4. Connect the 20 dB fixed attenuator and

Ch A In

connector using

a coaxial cable.

5. Click PPG/ED Ch1. Configure the settings as shown below:

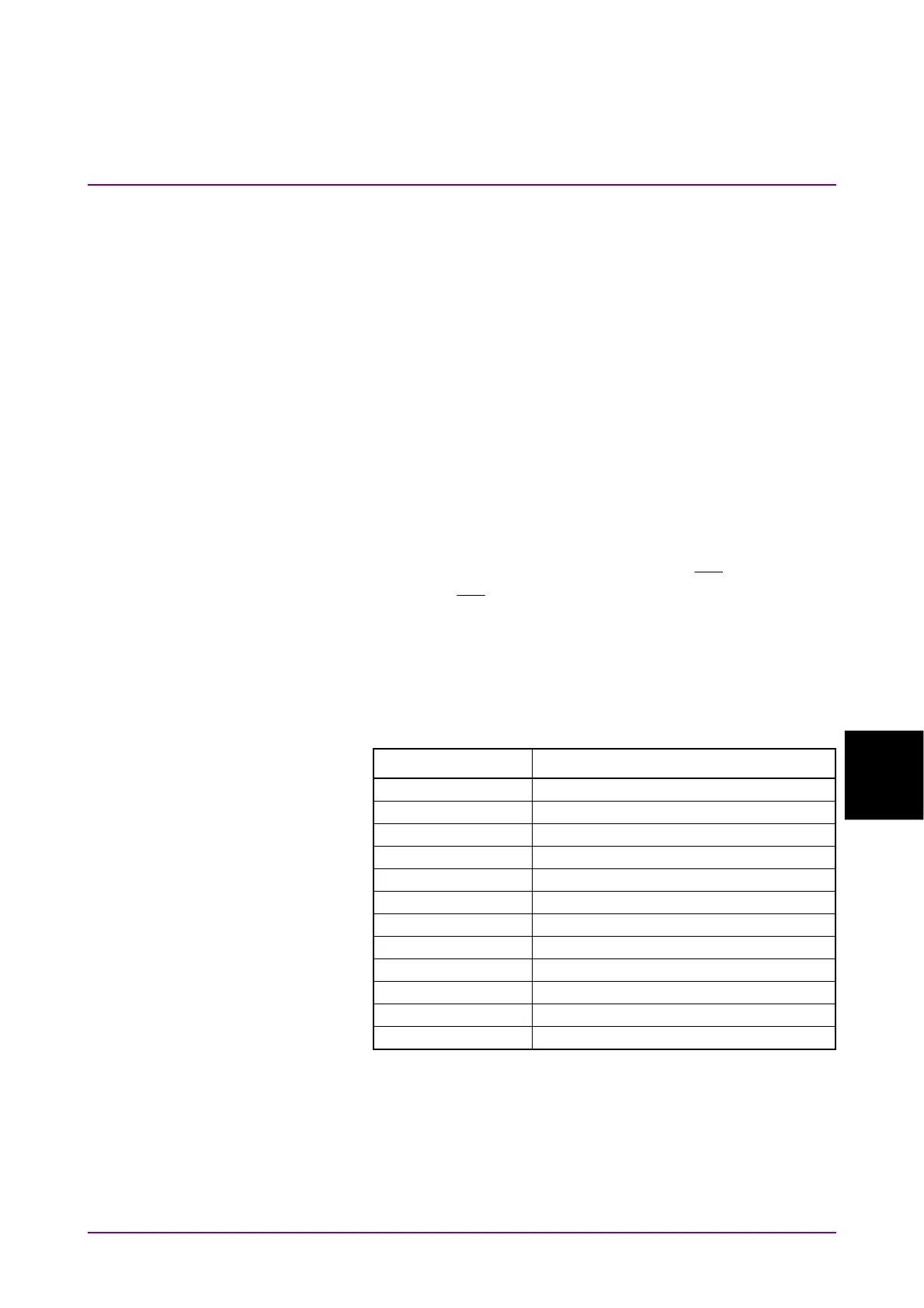

Item Setting Value

Reference Clock Internal

Symbol Rate 100GbE/4 (25.78125G), 0 ppm

Clock Output Ch1/2

PPG Amplitude 0.5

External ATT 0

Test Pattern (PPG) PRBS 2^31–1, POS

Test Pattern (ED) PRBS 2^31–1, POS

ED Input Condition Single-Ended Data

Threshold 0 mV

PPG Data/XData ON

Gating Cycle Single

Gating Period 45 s

Loading...

Loading...