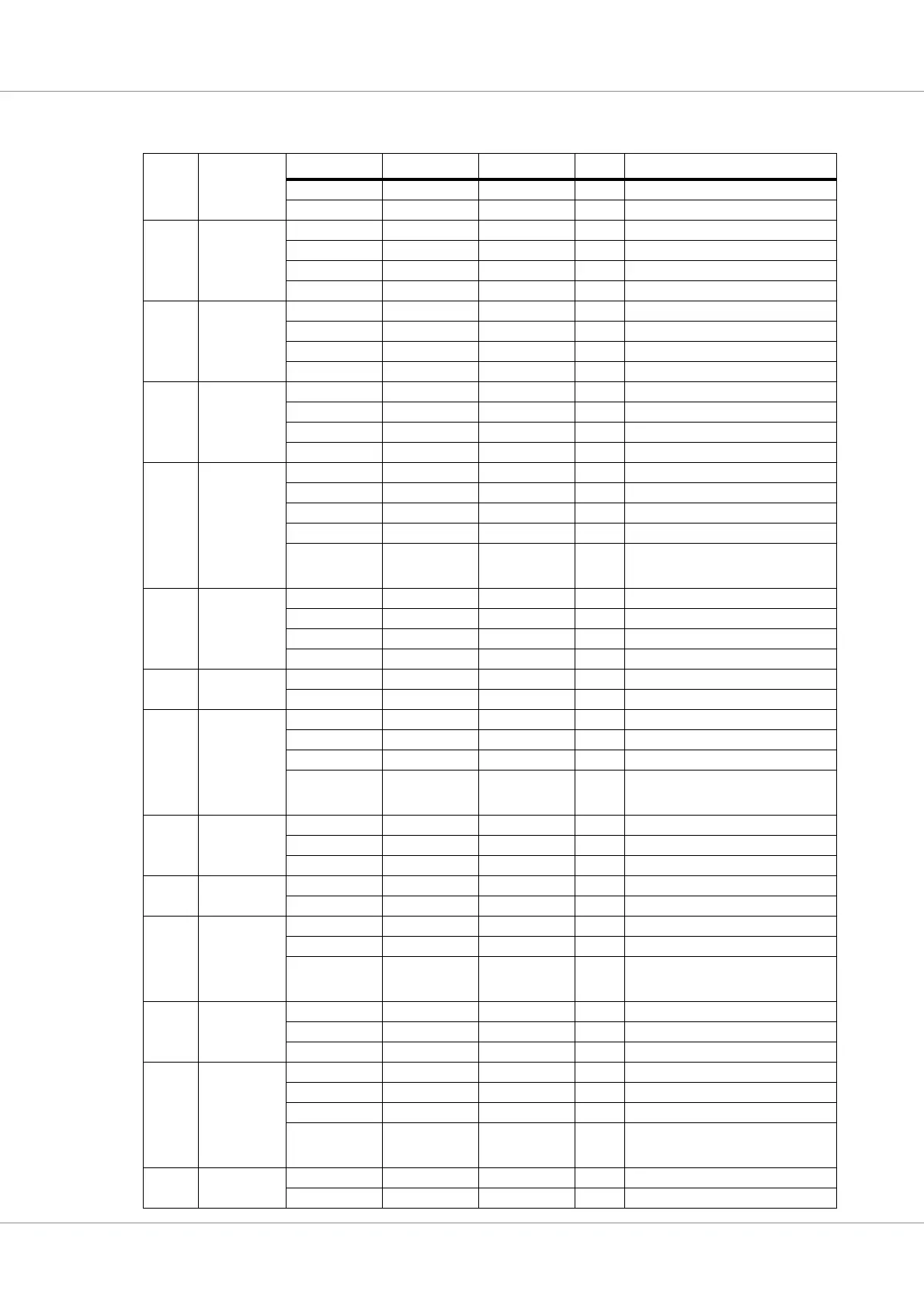

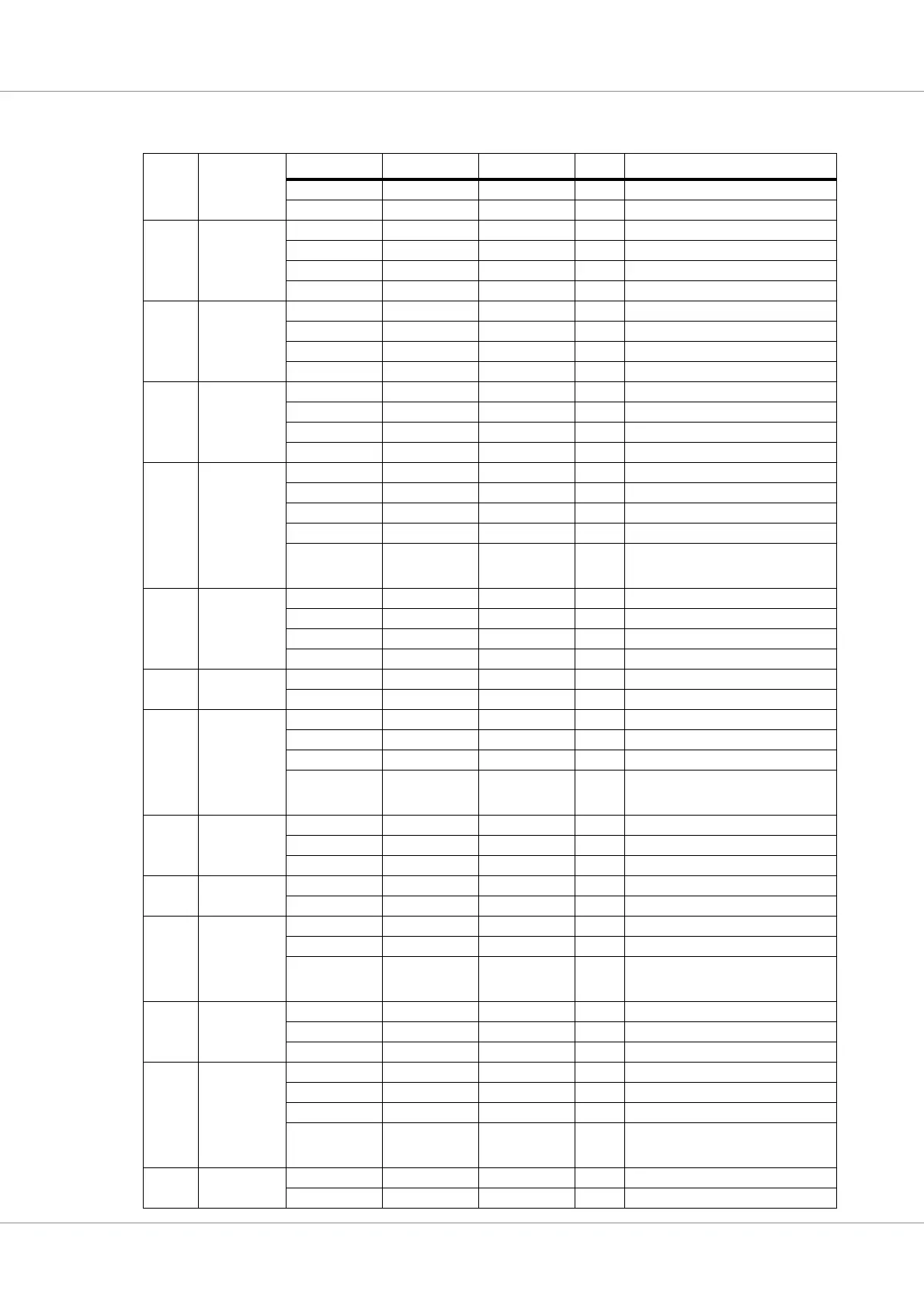

GR712RC-UM, Jun 2017, Version 2.9 25 www.cobham.com/gaisler

GR712RC

- High-Z Out Proprietary, enabled by CAN

GPIO[30] - High-Z In/Out GPIO 1 Register, bit 30

183 SWMX[34] 1553RXB High In MIL-STD-1553B Receive Positive B

TCRFAVL[1] High In Telecommand RF Available 1

RMCRSDV High In Ethernet Carrier Sense / Data Valid

GPIO[31] - In GPIO 1 Register, bit 31 (input only)

182 SWMX[35] 1553RXNB Low In MIL-STD-1553B Receive Negative B

TCCLK[2] Rising In Telecommand Clock 2

RMINTN Low In Ethernet Management Interrupt

GPIO[32] - In GPIO 2 Register, bit 0 (input only)

179 SWMX[36] 1553RXENB High High-Z Out MIL-STD-1553B Receive Enable B

A16MCS High High-Z Out ASCS MCS - TM start/stop signal

RMMDIO - High-Z In/Out Ethernet Media Interface Data

GPIO[33] - High-Z In/Out GPIO 2 Register, bit 1

178 SWMX[37] 1553TXB High High-Z Out MIL-STD-1553B Transmit Positive B

A16HS High High-Z Out ASCS HS - TM/TC serial clock

RMMDC - High-Z Out Ethernet Media Interface Clock

GPIO[34] - High-Z In/Out GPIO 2 Register, bit 2

SpaceWire clock

divisor registers

- In At reset, bits 8 and 0 in the clock divisor reg-

ister of the SpaceWire interfaces are set from

this input

177 SWMX[38] 1553CK - In MIL-STD-1553B Clock

TCD[2] - In Telecommand Data 2

RMRFCLK - In Ethernet Reference Clock

GPIO[35] - In GPIO 2 Register, bit 3 (input only)

176 SWMX[39] TCACT[2] High In Telecommand Active 2

GPIO[36] - In GPIO 2 Register, bit 4 (input only)

175 SWMX[40] 1553TXNB Low High-Z Out MIL-STD-1553B Transmit Negative B

A16DCS - High-Z Out ASCS DCS - Slave data out

GPIO[37] - High-Z In/Out GPIO 2 Register, bit 5

SpaceWire clock

divisor registers

- In At reset, bits 9 and 1 in the clock divisor reg-

ister of the SpaceWire interfaces are set from

this input

174 SWMX[41] 1553TXINHB High High-Z Out MIL-STD-1553B Transmit Inhibit B

A16MAS High High-Z Out ASCS MAS - TM start/stop signal

GPIO[38] - High-Z In/Out GPIO 2 Register, bit 6

173 SWMX[42] TCRFAVL[2] High In Telecommand RF Available 2

GPIO[39] - In GPIO 2 Register, bit 7 (input only)

172 SWMX[43] - High-Z Out Proprietary, enabled by CAN

GPIO[40] - High-Z In/Out GPIO 2 Register, bit 8

SpaceWire clock

divisor registers

- In At reset, bits 10 and 2 in the clock divisor reg-

ister of the SpaceWire interfaces are set from

this input

169 SWMX[44] SPICLK High-Z Out SPI Clock

SLO - High-Z Out SLINK Data Out

GPIO[41] - High-Z In/Out GPIO 2 Register, bit 9

166 SWMX[45] SPIMOSI - High-Z Out SPI Master Out Slave In

SLCLK High High-Z Out SLINK Clock

GPIO[42] - High-Z In/Out GPIO 2 Register, bit 10

SpaceWire clock

divisor registers

- In At reset, bits 11 and 3 in the clock divisor reg-

ister of the SpaceWire interfaces are set from

this input

165 SWMX[46] TCCLK[3] Rising In Telecommand Clock 3

GPIO[43] - In GPIO 2 Register, bit 11 (input only)

Table 6. I/O switch matrix pin description, defining the order of priority for outputs and input/outputs, with the highest

priority for each pin listed first.

Pin no. Pin name Pin function Polarity Reset value Dir. Description

Loading...

Loading...