GR712RC-UM, Jun 2017, Version 2.9 40 www.cobham.com/gaisler

GR712RC

4.2.5 Multiply instructions

The LEON processor supports the SPARC integer multiply instructions UMUL, SMUL UMULCC

and SMULCC. These instructions perform a 32x32-bit integer multiply, producing a 64-bit result.

SMUL and SMULCC performs signed multiply while UMUL and UMULCC performs unsigned

multiply. UMULCC and SMULCC also set the condition codes to reflect the result. The multiply

instructions are performed using a 16x16 hardware multiplier which is iterated four times. To improve

the timing, the 16x16 multiplier is provided with a pipeline stage.

4.2.6 Compare and Swap instruction (CASA)

GR712RC implements the SPARC V9 Compare and Swap Alternative (CASA) instruction. The

CASA operates as described in the SPARC V9 manual. The instruction is privileged but setting ASI =

0xA (user data) will allow it to be used in user mode.

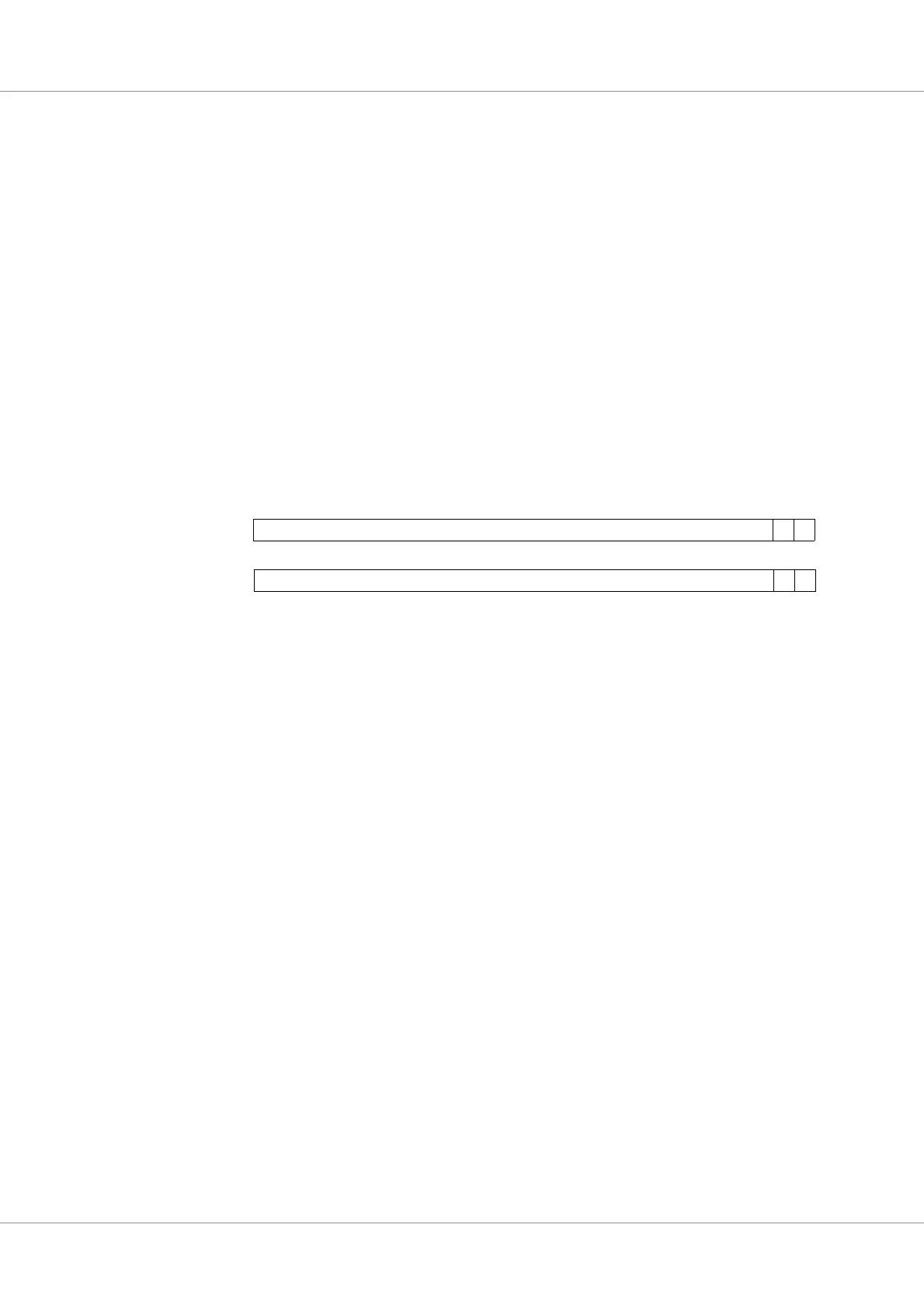

4.2.7 Hardware breakpoints

The integer unit includes two hardware breakpoints. Each breakpoint consists of a pair of application-

specific registers (%asr24/25 and %asr26/27), one with the break address and one with a mask:

Any binary aligned address range can be watched - the range is defined by the WADDR field, masked

by the WMASK field (WMASK[x] = 1 enables comparison). On a breakpoint hit, trap 0x0B is gener-

ated. By setting the IF, DL and DS bits, a hit can be generated on instruction fetch, data load or data

store. Clearing these three bits will effectively disable the breakpoint function.

4.2.8 Instruction trace buffer

The instruction trace buffer consists of a circular buffer that stores executed instructions. The trace

buffer operation is controlled through the debug support interface, and does not affect processor oper-

ation. The size of the trace buffer is 4 KiB, equivalent to 256 lines. The trace buffer is 128 bits wide,

and stores the following information:

• Instruction address and opcode

• Instruction result

• Load/store data and address

• Trap information

• 30-bit time tag

The operation and control of the trace buffer is further described in section 9.4. Note that in

GR712RC, each processor has its own trace buffer allowing simultaneous tracing of both instruction

streams.

01231

DL

WADDR[31:2]

%asr24, %asr26

0231

DS

WMASK[31:2]

%asr25, %asr27

Figure 4. Watch-point registers

IF

Loading...

Loading...