GR712RC-UM, Jun 2017, Version 2.9 41 www.cobham.com/gaisler

GR712RC

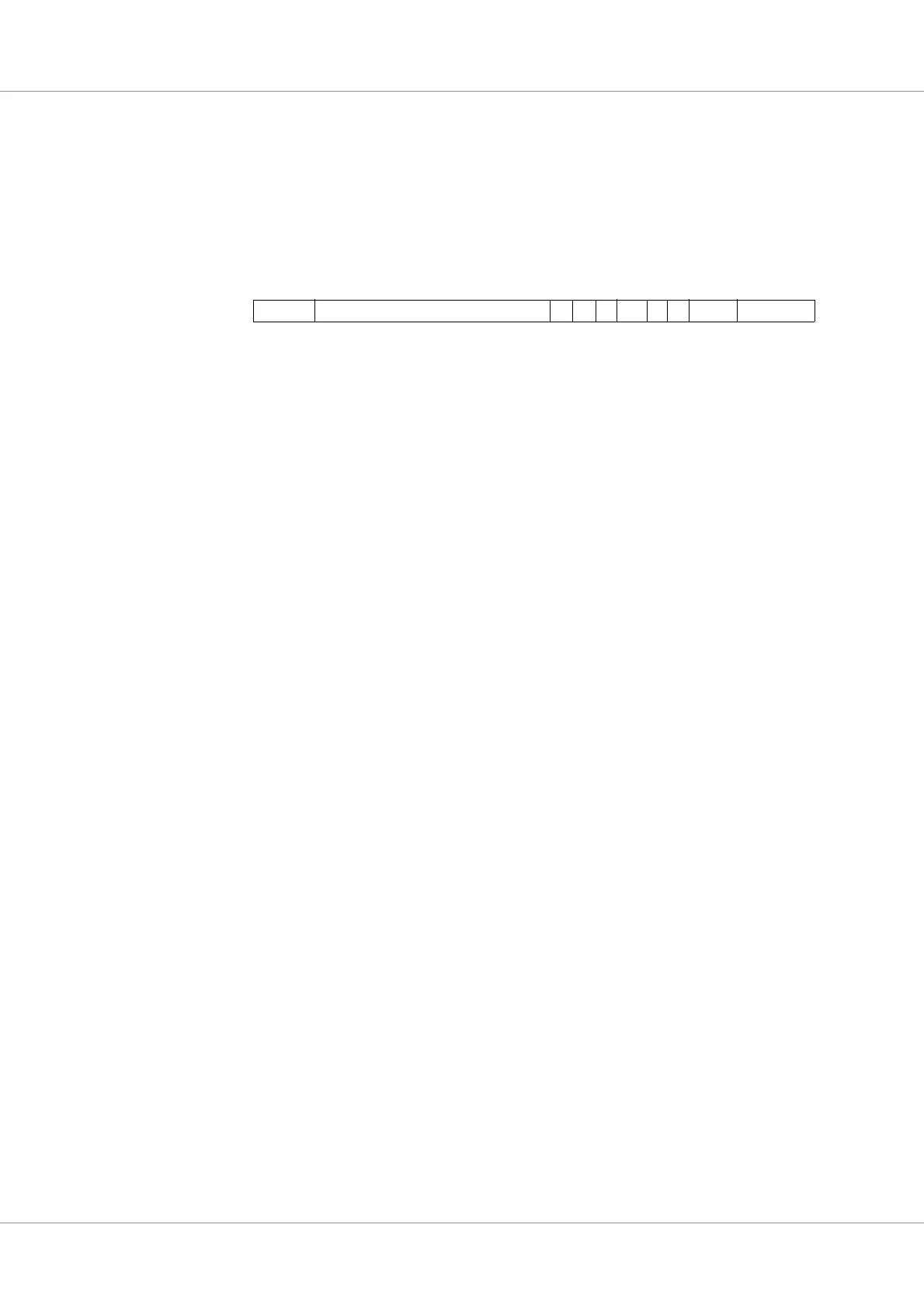

4.2.9 Processor configuration register

The application specific register 17 (%asr17) provides information on how various configuration

options were set during synthesis. This can be used to enhance the performance of software, or to sup-

port enumeration in multi-processor systems. The register can be accessed through the RDASR

instruction, and has the following layout:

Field Definitions:

[31:28]: Processor index. In multi-processor systems, each LEON core gets a unique index to support enumeration. The

value in this field is 0 for core0 and 1 for core1.

[14]: Disable write error trap (DWT). When set, a write error trap (tt = 0x2b) will be ignored. Set to zero after reset.

[13]: Single-vector trapping (SVT) enable. If set, will enable single-vector trapping. Set to zero after reset.

[11:10]: FPU option. Hardcoded to 1 (GRFPU)

[8]: If set, the SPARC V8 multiply and divide instructions are available. Hardcoded to 1.

[7:5]: Number of implemented watchpoints. Hardcoded to 2

[4:0]: Number of implemented registers windows corresponds to NWIN+1. Hardcoded to 7.

04831

RESERVED

%asr17

Figure 5. LEON3 configuration register (%asr17)

00111

28

INDEX

75

010

1

9

0

12 11 10

10

0

13

SVDW

14

Loading...

Loading...