GR712RC-UM, Jun 2017, Version 2.9 39 www.cobham.com/gaisler

GR712RC

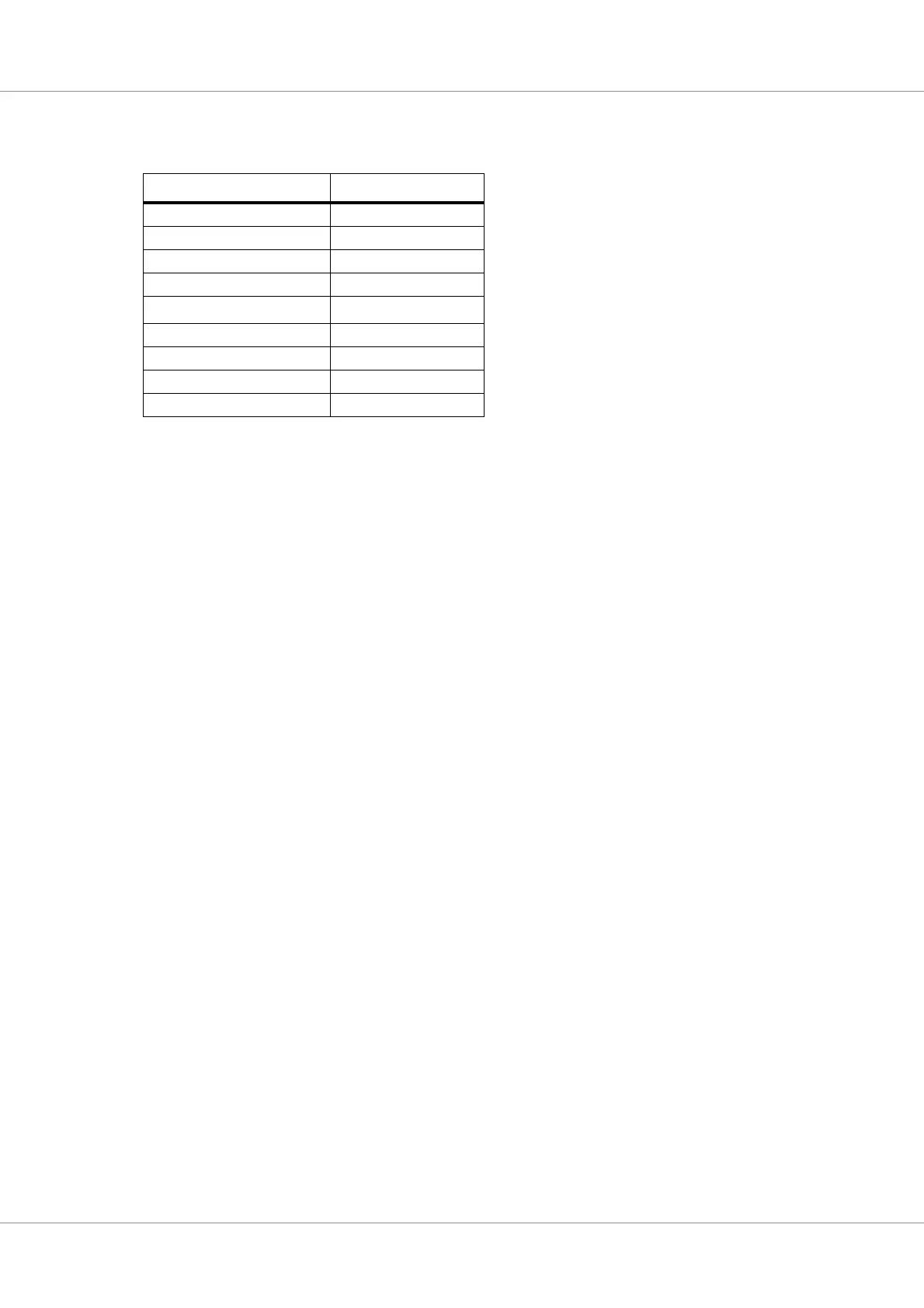

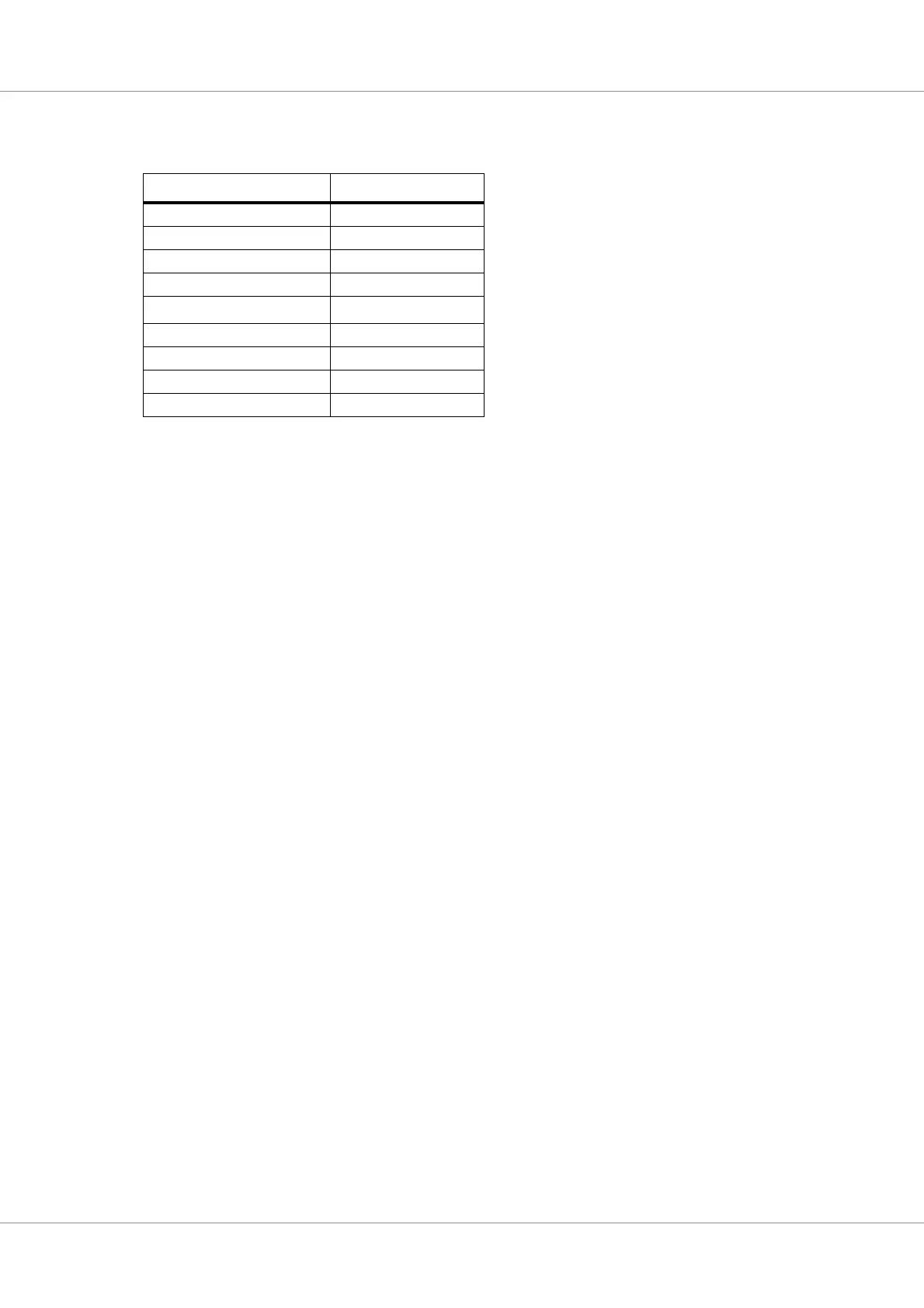

Table 14 lists the cycles per instruction (assuming cache hit and no icc or load interlock):

4.2.3 SPARC Implementor’s ID

Gaisler Research is assigned number 15 (0xF) as SPARC implementor’s identification. This value is

hard-coded into bits 31:28 in the %psr register. The version number for LEON3 is 3, which is hard-

coded in to bits 27:24 of the %psr.

4.2.4 Divide instructions

Full support for SPARC V8 divide instructions is provided (SDIV, UDIV, SDIVCC & UDIVCC). The

divide instructions perform a 64-by-32 bit divide and produce a 32-bit result. Rounding and overflow

detection is performed as defined in the SPARC V8 standard.

Table 14. Instruction timing

Instruction Clock Cycles

JMPL, RETT 3

Double load 2

Single store 2

Double store 3

SMUL/UMUL

4

SDIV/UDIV 35

Taken Trap 5

Atomic load/store 3

All other instructions 1

Loading...

Loading...