Hub Interface Routing

R

128 Intel

®

Pentium

®

4 Processor / Intel

®

850 Chipset Family Platform Design Guide

8.2 8-Bit Hub Interface Routing Guidelines

This section describes the routing guidelines for the 8-bit hub interface. This hub interface

connects the ICH2 to the MCH. This interface supports normal buffer mode. When the buffers are

configured for normal mode, the trace impedance must equal 60 Ω

± 15%.

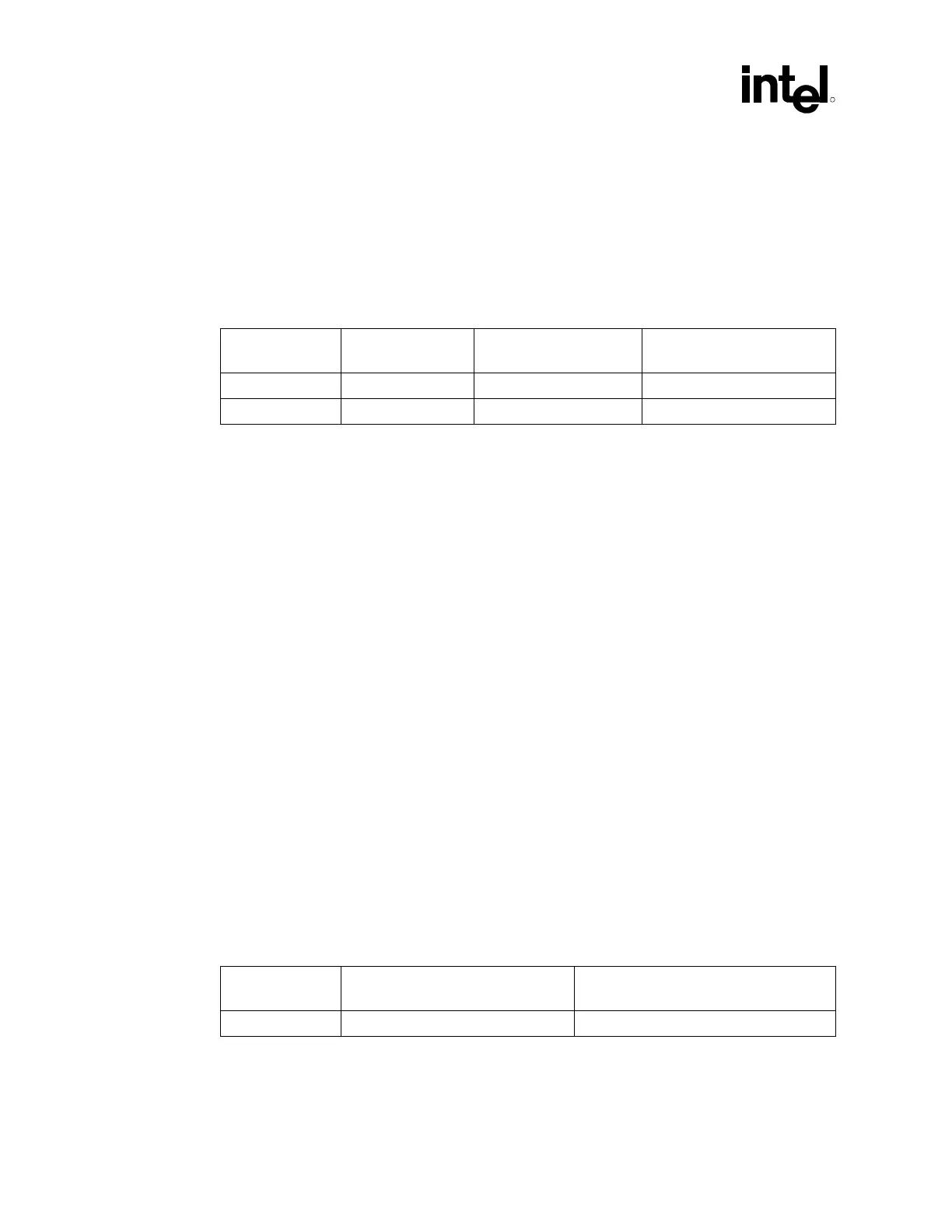

Table 30. 8-Bit Hub Interface Buffer Configuration Setting

Component Hub Interface

Buffer Mode

Trace Impedance Strap

ICH2 Normal 60 Ω HLCOMP pulled to VCC1_8

1

MCH Normal 60 Ω Default

NOTE:

1

Refer to Section 8.2.4 for the specific resistor value.

8.2.1 8-Bit Hub Interface Data Signals

The 8-bit hub interface data signal traces should be routed 5 mils wide with 20 mils trace spacing

(5 on 20). These signals can be routed 5 on 15 for navigation around components or mounting

holes. To break out of the MCH and ICH2 package, the hub interface data signals can be routed

5 on 5. The signal must be separated to 5 on 20 within 300 mils of the package. The maximum hub

interface data signal trace length in normal buffer mode is 6 inches. Each data signal must be

matched within ±0.1 inches of the HL_STB differential pair. There is no explicit matching

requirement between the individual data signals.

8.2.2 8-Bit Hub Interface Strobe Signals

The hub interface strobe signals should be routed 5 mils wide with 20 mils trace spacing (5 on 20).

This strobe pair should have a minimum of 20 mils spacing from any adjacent signals. The

maximum length for the strobe signal in normal mode is 6 inches. Each strobe signal must be the

same length, and each data signal must be matched within ±0.1 inches of the strobe signals.

8.2.3 8-Bit Hub Interface HIREF Generation/Distribution

HIREF is the hub interface reference voltage. The HIREF voltage requirement must be set

appropriately for proper operation. See Table 31 for the HIREF voltage specifications for normal

buffer mode and the associated resistor recommendations for the voltage divider circuit.

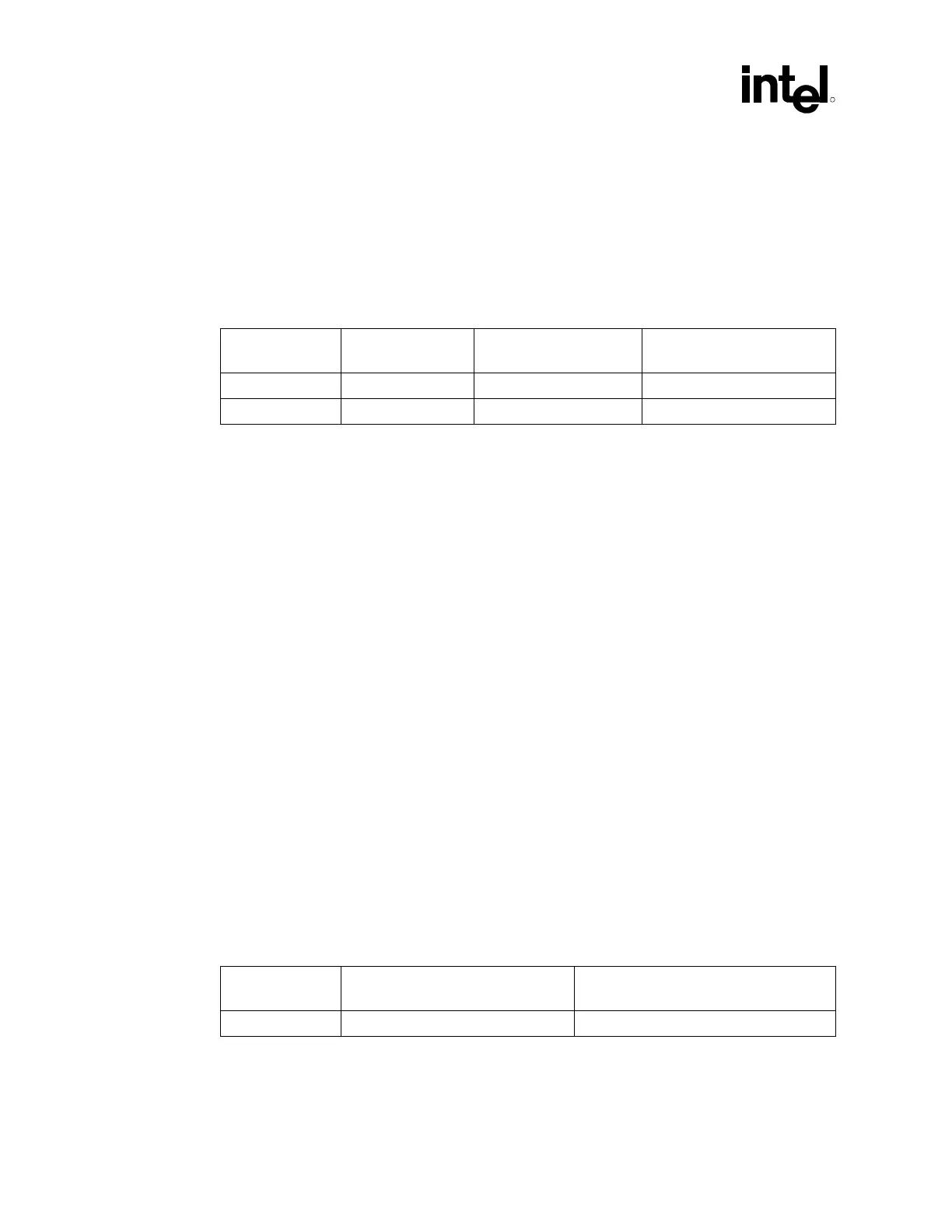

Table 31. 8-Bit Hub Interface HUBREF Generation Circuit Specifications

Buffer Mode HIREF Voltage Specification (V) Recommend Resistor Values for the

HIREF Divider Circuit (ohm)

Normal 1/2 VCC1_8 ± 2% R1 = R2 = 150 ± 1%

The single HIREF divider should not be located more than 3.5 inches away from either MCH or

ICH2. If the single HIREF divider is located more than 3.5 inches away, then the locally generated

hub interface reference dividers should be used instead.

Loading...

Loading...