Memory Interface Routing

R

Intel

®

Pentium

®

4 Processor / Intel

®

850 Chipset Family Platform Design Guide 99

The amount of capacitance needed depend on the length the signals have to travel though the

RIMM connector pin (i.e., a signal on the bottom layer has to travel though more of the RIMM

connector pin than a signal on the top layer). This can be achieved on the motherboard by adding a

copper tab to the specified RSL pins at each connector.

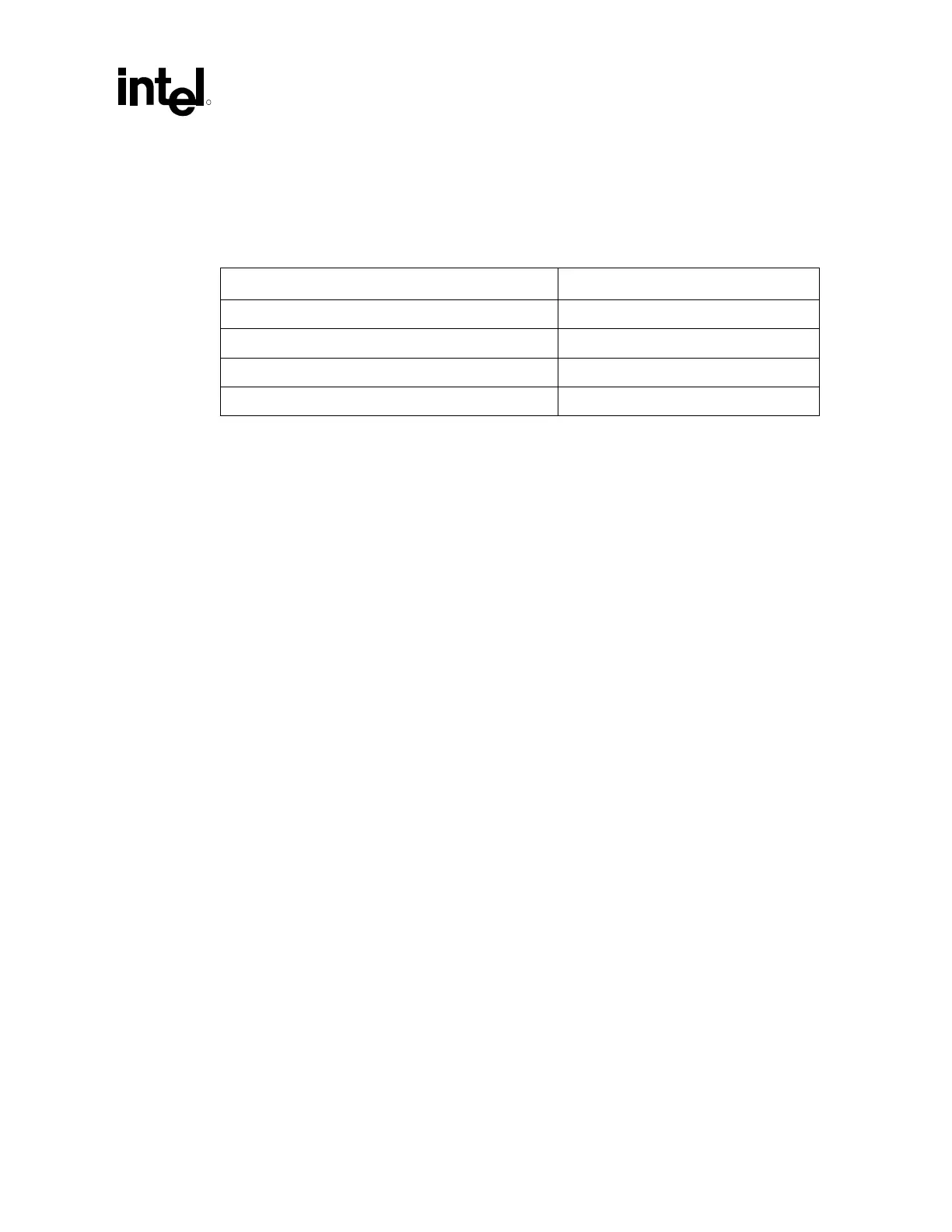

Table 23. RSL and Clocking Signal Rambus RIMM* Connector Capacitance Requirement

RSL and Clocking Signal Routing Layer Capacitance (pF)

1

Top 0.8

Inner 1 0.9

Inner 2 1.23

Bottom 1.35

NOTE:

1

These numbers are based on a six layer stack-up.

The copper tab area for the recommended stack-up was determined through simulation. The

amount of capacitance required is determined by the layer the RSL or clocking signal is routed on.

The placement of the copper tabs can be on any signal layer, independent of the layer on which the

RSL signal is routed.

Capacitance for a different stack-up assuming a 62mil board thickness can be computed by linear

interpolation. The equation for determining the amount of capacitance needed on any stripline

layer can be found by Equation 6.

Equation 6. Calculation for a Stripline C-tab

Ctab

LayerX

= .8pF + (1.35pF -.8pF)(X/62)

Where

• X is the distance in mils from the top of the board to the stripline signal layer in which the

RSL or clocking signals are routed on.

Equation 7 is an approximation that can be used for calculating copper tab area on the outer layer.

Equation 7. Copper Tab Capacitance Calculation

Length * Width = Area = [C

plate

* Thickness of prepreg] / [ε

0

* ε

r

* 1.1]

Where:

• C

plate

= Capacitance of the plates

• ε

0

= 2.25 x 10

-16

Farads/mil

• ε

r

= Relative dielectric constant of prepreg material

• Thickness of prepreg = Stack-up dependent

• Length, Width = Dimensions in mils of copper plate to be added

• Factor of 1.1 accounts for fringe capacitance.

Loading...

Loading...