I/O Controller Hub 2

R

Intel

®

Pentium

®

4 Processor / Intel

®

850 Chipset Family Platform Design Guide 147

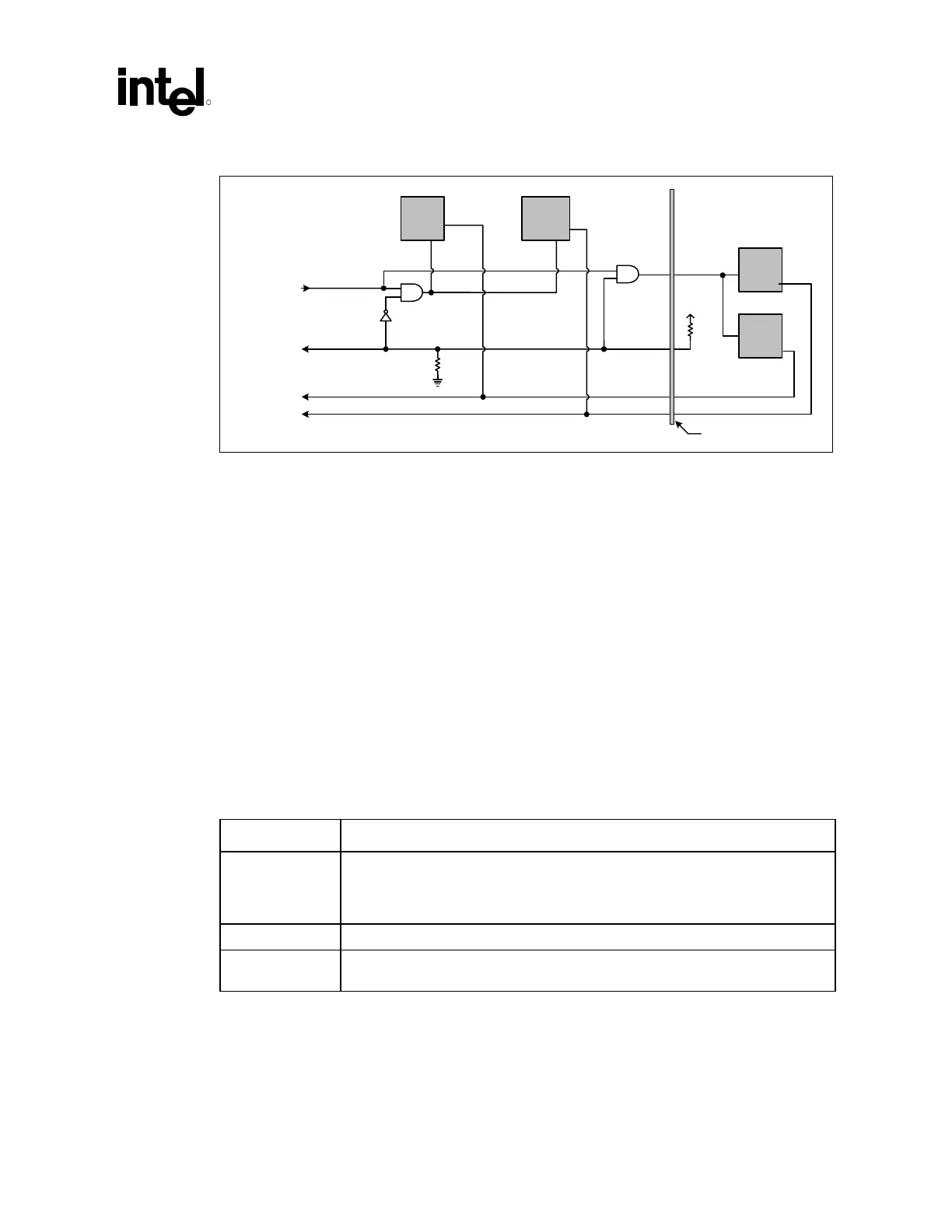

Figure 103. CDC_DN_ENAB# Support for Two-Codecs on Motherboard / Two-Codecs on CNR

Codec A

RESET#

SDATA_IN

Codec C

RESET#

SDATA_ IN

AC97_RESET#

Vcc

CDC_DN_ENAB#

CNR BoardMotherboard

R

A

10kohms

R

B

1kohms

To General

Purpose Input

From AC '97

Controller

CNR Connector

To AC '97

Digital

Controller

SDATA_IN0

SDATA_IN1

Codec D

RESET#

SDATA_ IN

Codec B

RESET#

SDATA_IN

Circuit Notes

• All CNR designs include resistor R

B

. The value of R

B

is either 1 kΩ or 100 kΩ, depending on

the intended functionality of the CNR (whether or not it intends to be the primary/controlling

codec).

• Any CNR with two codecs must implement R

B

with value 1 kΩ. If there is one Codec, use a

100 kΩ pull-up resistor. A CNR with zero codecs must not stuff R

B

. If implemented, R

B

must

be connected to the same power well as the codec so that it is valid whenever the codec has

power.

• A motherboard with one or more codecs down must implement R

A

with a value of 10 kΩ.

• The CDC_DN_ENAB# signal must be run to a GPI so that the BIOS can sense the state of the

signal. CDC_DN_ENAB# is required to be connected to a GPI; a connection to a GPIO is

strongly recommended for testing purposes.

Table 34. Signal Descriptions

Signal Description

CDC_DN_ENAB# When low, indicates that the codec on the motherboard is enabled and primary on the

AC97 Interface. When high, indicates that the motherboard codec(s) must be

removed from the AC ’97 Interface (held in reset), because the CNR codec(s) will be

the primary device(s) on the AC ’97 Interface.

AC97_RESET# Reset signal from the AC ’97 Digital Controller (ICH2).

SDATA_INn AC ’97 serial data from an AC ’97-compliant codec to an AC ’97-compliant controller

(i.e., the ICH2).

Loading...

Loading...