I/O Controller Hub 2

R

140 Intel

®

Pentium

®

4 Processor / Intel

®

850 Chipset Family Platform Design Guide

9.3 Intel

®

AC’97

The ICH2 implements an AC’97 2.1 compliant digital controller. Any codec attached to the ICH2

AC-link must be AC’97 2.1 compliant as well. Contact your codec vendor for information on 2.1

compliant products. The AC’97 2.1 specification is on the Intel website:

http://developer.intel.com/pc-supp/platform/ac97/index.htm

The AC-link is a bi-directional, serial PCM digital stream. It handles multiple input and output

data streams, as well as control register accesses, employing a time division multiplexed (TDM)

scheme. The AC-link architecture provides for data transfer through individual frames transmitted

in a serial fashion. Each frame is divided into 12 outgoing and 12 incoming data streams, or slots.

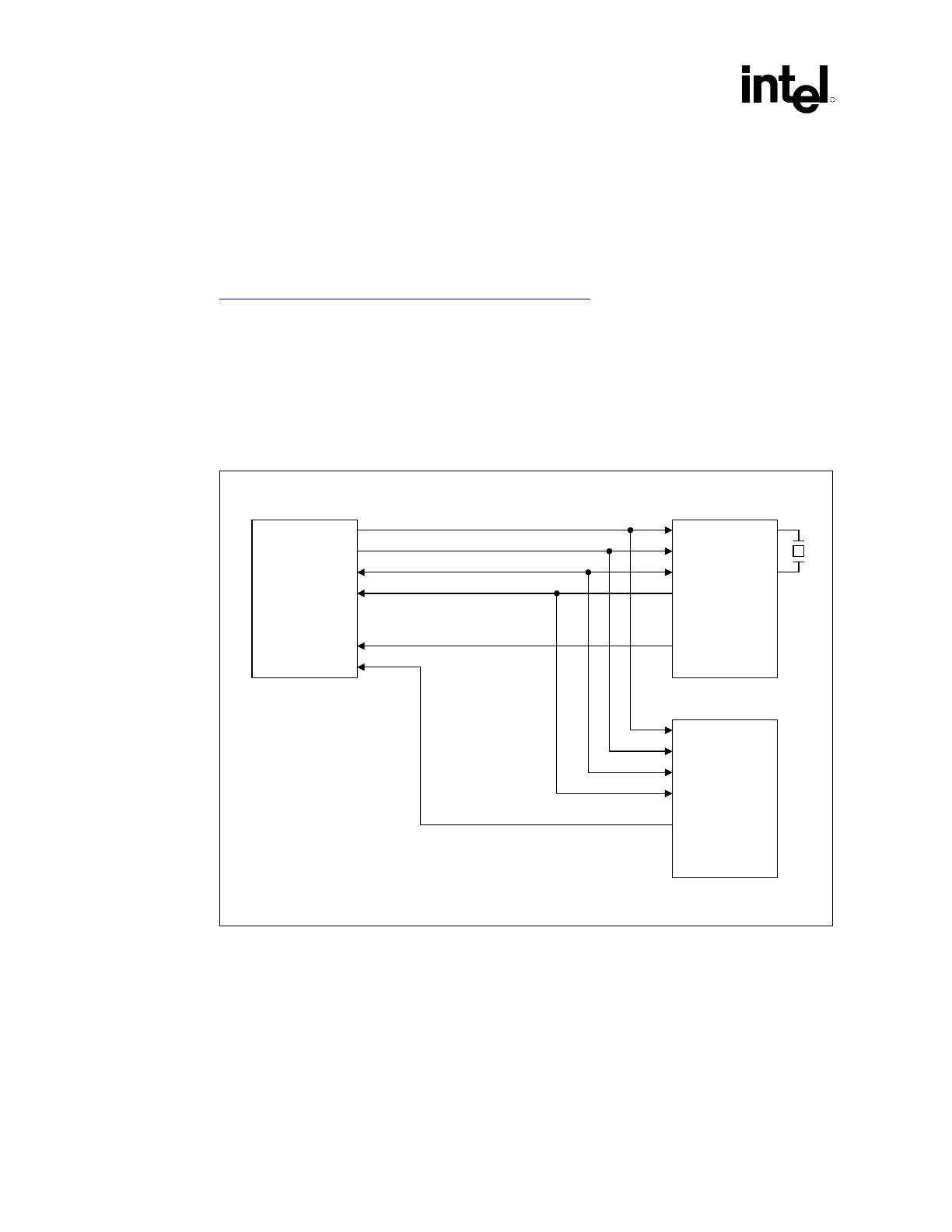

The architecture of the ICH2 AC-link allows a maximum of two codecs to be connected. Figure 92

shows a two-codec topology of the AC-link for the ICH2.

Figure 92. Intel

®

ICH2 AC’97 - Codec Connection

AC '97 2.1

controller section

of ICH2

Digital AC '97

2.1 controller

Primary codec

Secondary codec

AC / MC

AC / MC / AMC

AC97_ICH2-codec_conn

SDIN 0

SDIN 1

RESET#

SDOUT

SYNC

BIT_CLK

In a lightly loaded system (e.g., single codec down), AC’97 signal integrity should be evaluated to

confirm that the signal quality on the link is acceptable to the codec used in the design. A series

resistor at the driver and a capacitor at the codec can be implemented in order to compensate for

any signal integrity issues. The values used will be design dependent and should be verified for

correct timings. The ICH2 AC-link output buffers are designed to meet the AC’97 2.1

specification with the specified load of 50 pF.

The ICH2 supports the following combinations of codecs:

Loading...

Loading...