Network and Remote Operation

R&S

®

FSVA3000/ R&S

®

FSV3000

677User Manual 1178.8520.02 ─ 01

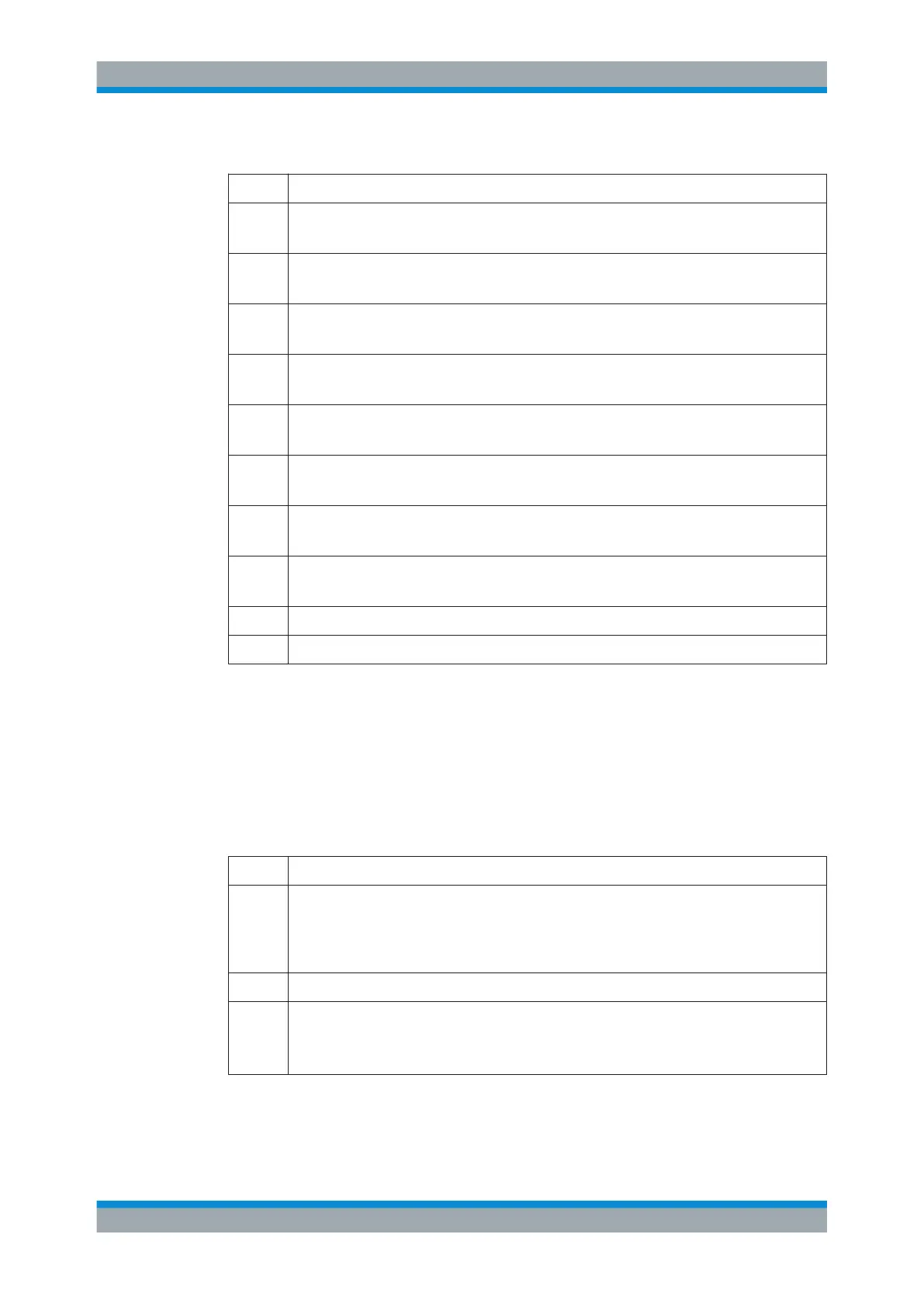

Table 13-16: Meaning of the bits used in the STATus:QUEStionable:LMARgin register

Bit No. Meaning

0 LMARgin 1 FAIL

This bit is set if limit margin 1 is violated.

1 LMARgin 2 FAIL

This bit is set if limit margin 2 is violated.

2 LMARgin 3 FAIL

This bit is set if limit margin 3 is violated.

3 LMARgin 4 FAIL

This bit is set if limit margin 4 is violated.

4 LMARgin 5 FAIL

This bit is set if limit margin 5 is violated.

5 LMARgin 6 FAIL

This bit is set if limit margin 6 is violated.

6 LMARgin 7 FAIL

This bit is set if limit margin 7 is violated.

7 LMARgin 8 FAIL

This bit is set if limit margin 8 is violated.

8 to 14 Not used

15 This bit is always 0.

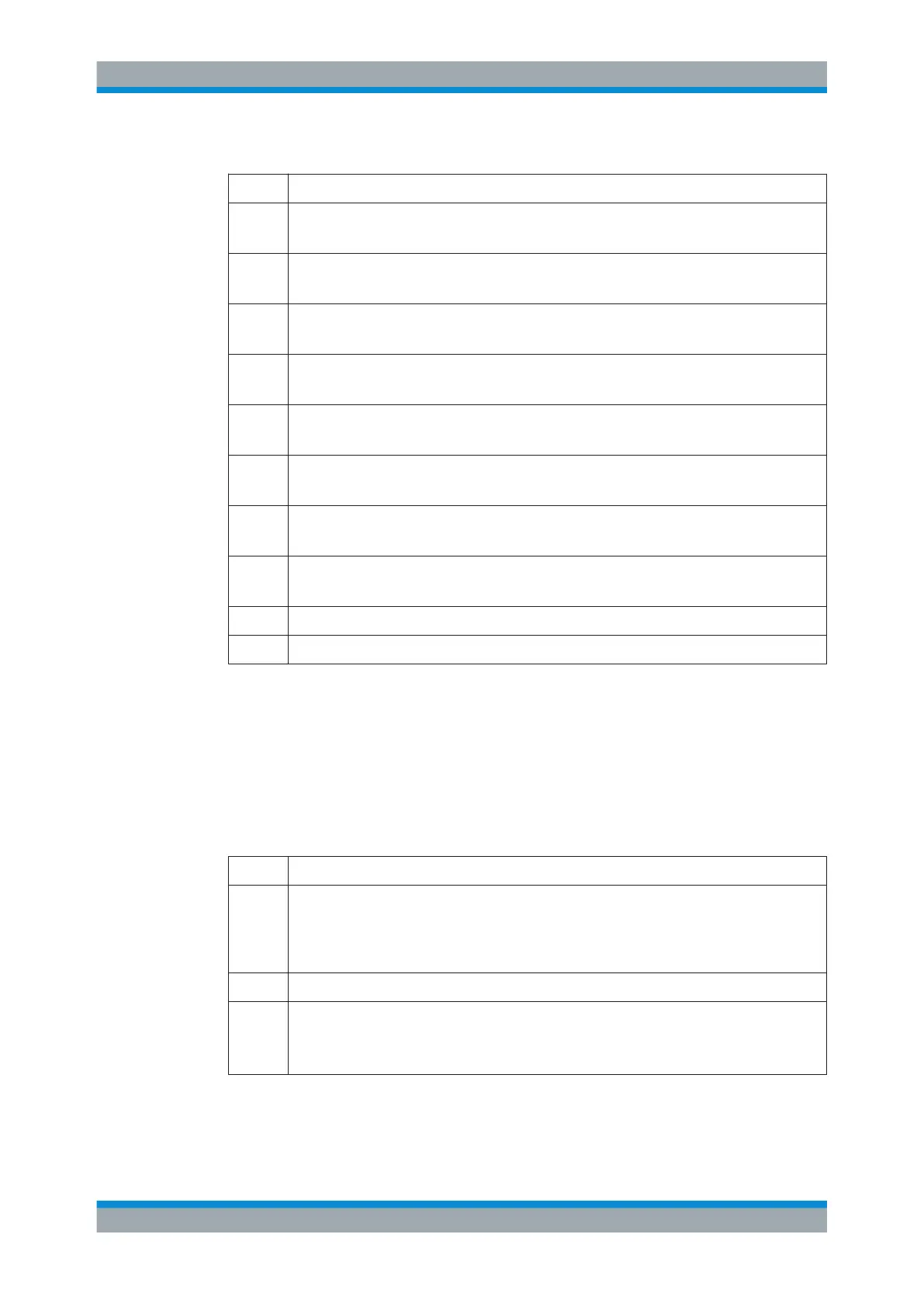

STATus:QUEStionable:POWer Register

The STATus:QUEStionable:POWer register contains information about possible

overload situations that may occur during operation of the R&S FSV/A. A separate

power register exists for each active channel.

You can read out the register with STATus:QUEStionable:POWer:CONDition? or

STATus:QUEStionable:POWer[:EVENt]?

Table 13-17: Meaning of the bits used in the STATus:QUEStionable:POWer register

Bit No. Meaning

0 OVERload

This bit is set if an overload occurs at the RF input, causing signal distortion but not yet causing

damage to the device.

The R&S FSV/A displays the keyword "RF OVLD".

1 Unused

2 IF_OVerload

This bit is set if an overload occurs in the IF path.

The R&S FSV/A displays the keyword "ADC OVLD".

Remote Control Basics

Loading...

Loading...