GR712RC-UM, Jun 2017, Version 2.9 177 www.cobham.com/gaisler

GR712RC

23:0 SLINK NULL Word (NULLWORD) - This register contains the value of the NULL word that the

core transmits during inactivity. Bits 23:0 in this register constitutes bits 24:1 in the SLINK data

word. The parity bit is calculated by the core and appended at the end of the word.

Reset value: 0x00000000

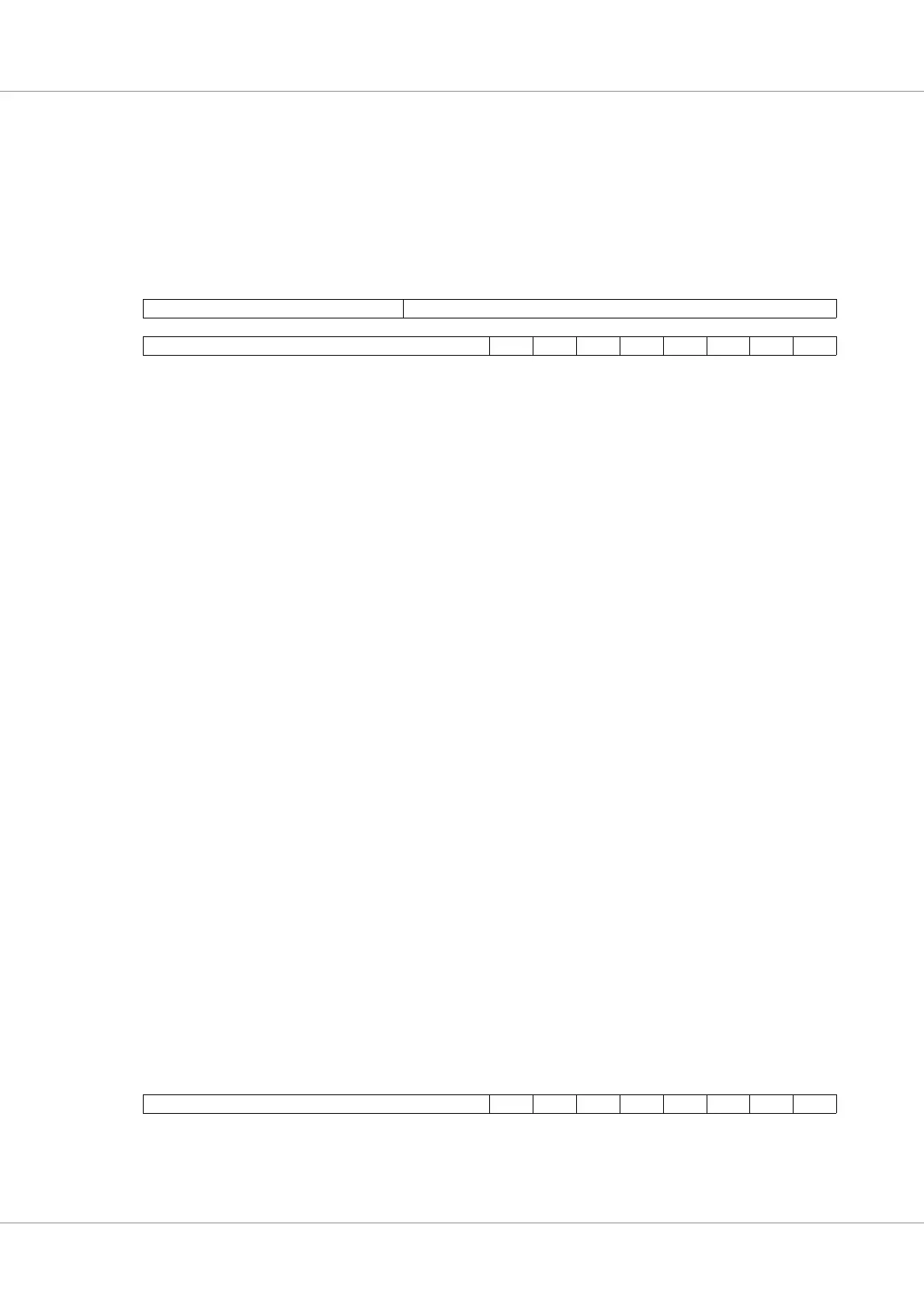

Table 189. GRSLINK Status register

31 26 25 16

RESERVED SI

15 876543210

RESERVED PERR AERR ROV RNE TNF SC SA SRX

31:26 RESERVED

25:16 SEQUENCE Index (SI) - This fields contains the index of the next element to write to the B array

during SEQUENCE operation. With the help of this field software can monitor the progress

SEQUENCE operations. Software can also determine that SI elements were written back if the

SEQUENCE was aborted. Note that the field holds a maximum value of 1023. If the SEQUENCE is

1024 operations long this counter will wrap on the last element. In this case software must check if

the SC bit is set to determine if the core transferred 0 or 1024 elements. This field is read only.

15: 8 RESERVED

7 Parity Error (PERR) - This bit is set when a parity error is detected. The bit is cleared by writing ‘1’

to this position.

6 AMBA ERROR (AERR) - This bit is set to ‘1’ when the core receives an ERROR response to a

transfer on the AMBA AHB bus. This event aborts any ongoing SEQUENCE and clears bit 1 in the

Control register and bit 1 in the Status register. This bit is considered to get set even if it already has

the value ‘1’ and an AMBA ERROR event will always generate a interrupt if ARRE (bit 6) in the

mask register is set.

5 Receive Overflow (ROV) - This bit is set to ‘1’ when the core receives a word and the receive queue

is full. The incoming word is discarded. This is a critical error since a master system must guarantee

that words can be received.

4 Receive Not Empty (RNE) - This bit is ‘1’ when the receive queue contains a word. This read only

bit is automatically cleared when the receive queue is empty.

3 Transmit Not Full (TNF) - This bit is ‘1’ when the core has one or more free slots in the transmit

queue. When this bit is set software may write a new word into the Transmit register. This bit is read

only.

2 SEQUENCE Completed (SC) - This bit is set to ‘1’ when the core has performed the READ/WRITE

operation described at the end of the SEQUENCE array. This bit is cleared by writing ‘1’ to this

position.

1 SEQUENCE Aborted (SA) - This bit is set to ‘1’ if SEQUENCE operation was aborted by software

setting the Abort SEQUENCE (AS) bit in the control register. If this bit is set the core did not write

back results for all SLEN operations. This bit is cleared by writing ‘1’ to this position.

0 SLINK Word Received (SRX) - This bit is set when the master has accepted a single word from an

IO card and is not set if the core receives a word with parity error or if the reception of a word leads

to a receive overflow. This bit is cleared by writing ‘1’ to this position.

Reset value: 0x00000008

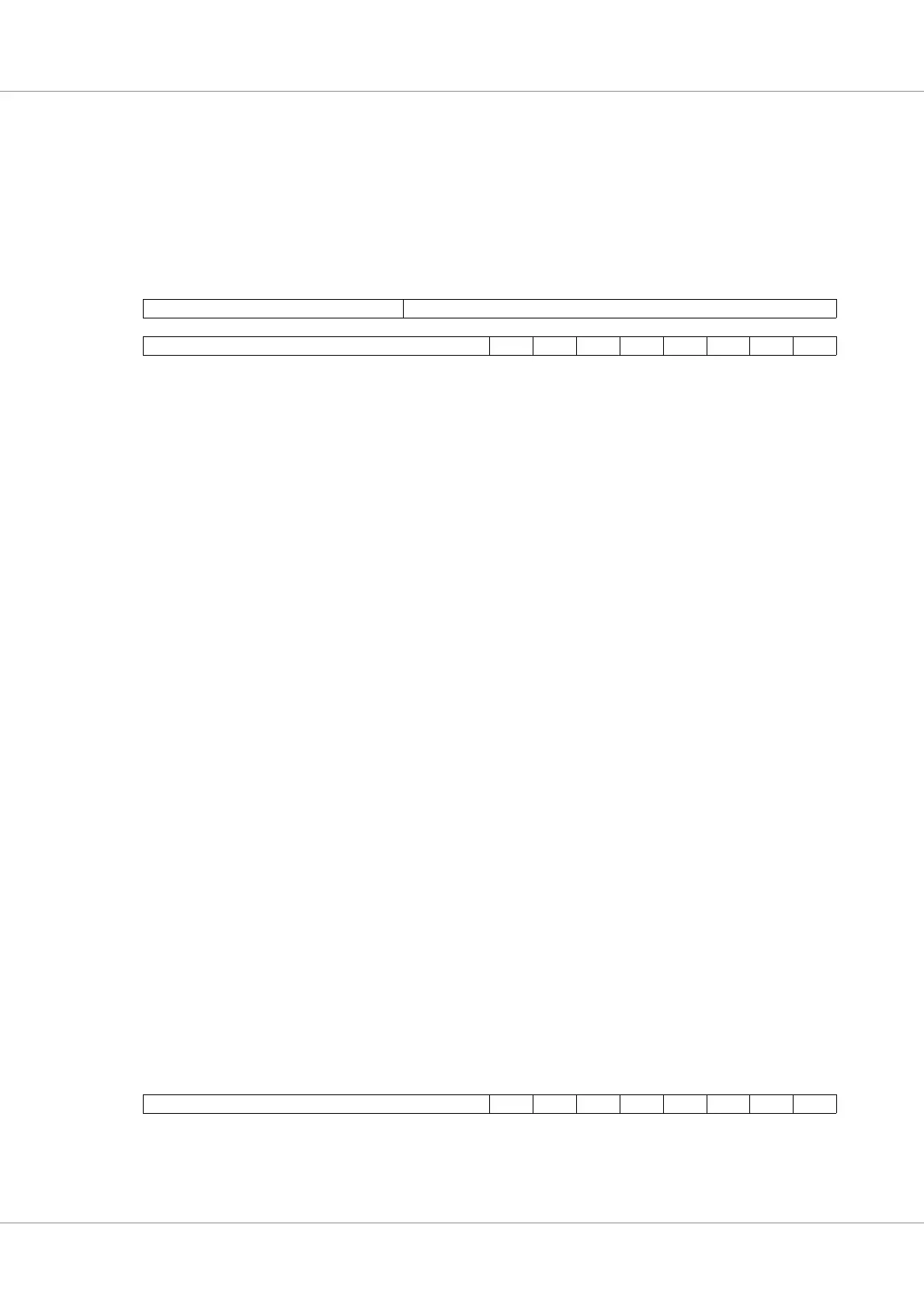

Table 190. GRSLINK Interrupt Mask register

31 876543210

RESERVED SERRE AERRE ROVE RNEE TNFE SCE SAE SRXE

31:7 RESERVED

7 Parity Error Enable (PERRE) - When this bit is set to ‘1’ the core will generate an interrupt when a

parity error is detected.

Table 188. GRSLINK NULL word register

Loading...

Loading...