621

A.2.54 Port A Data Register (PADR) Port A

• Start Address: H'5FFFFC0

• Bus Width: 8/16/32

Register Overview:

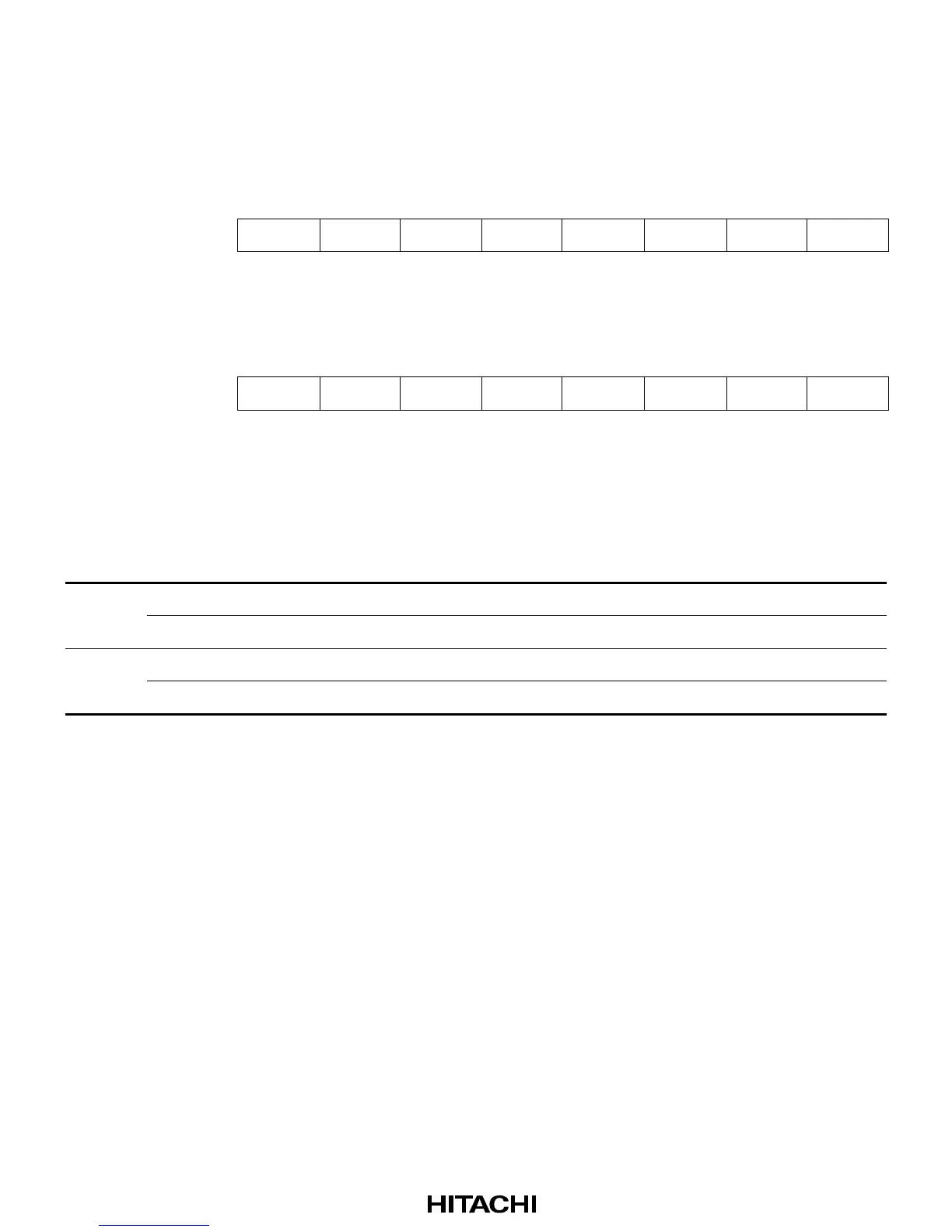

Bit: 15 14 13 12 11 10 9 8

Bit name: PA15DR PA14DR PA13DR PA12DR PA11DR PA10DR PA9DR PA8DR

Initial value: 0 0 0 0 0 0 0 0

R/W: R/W R/W R/W R/W R/W R/W R/W R/W

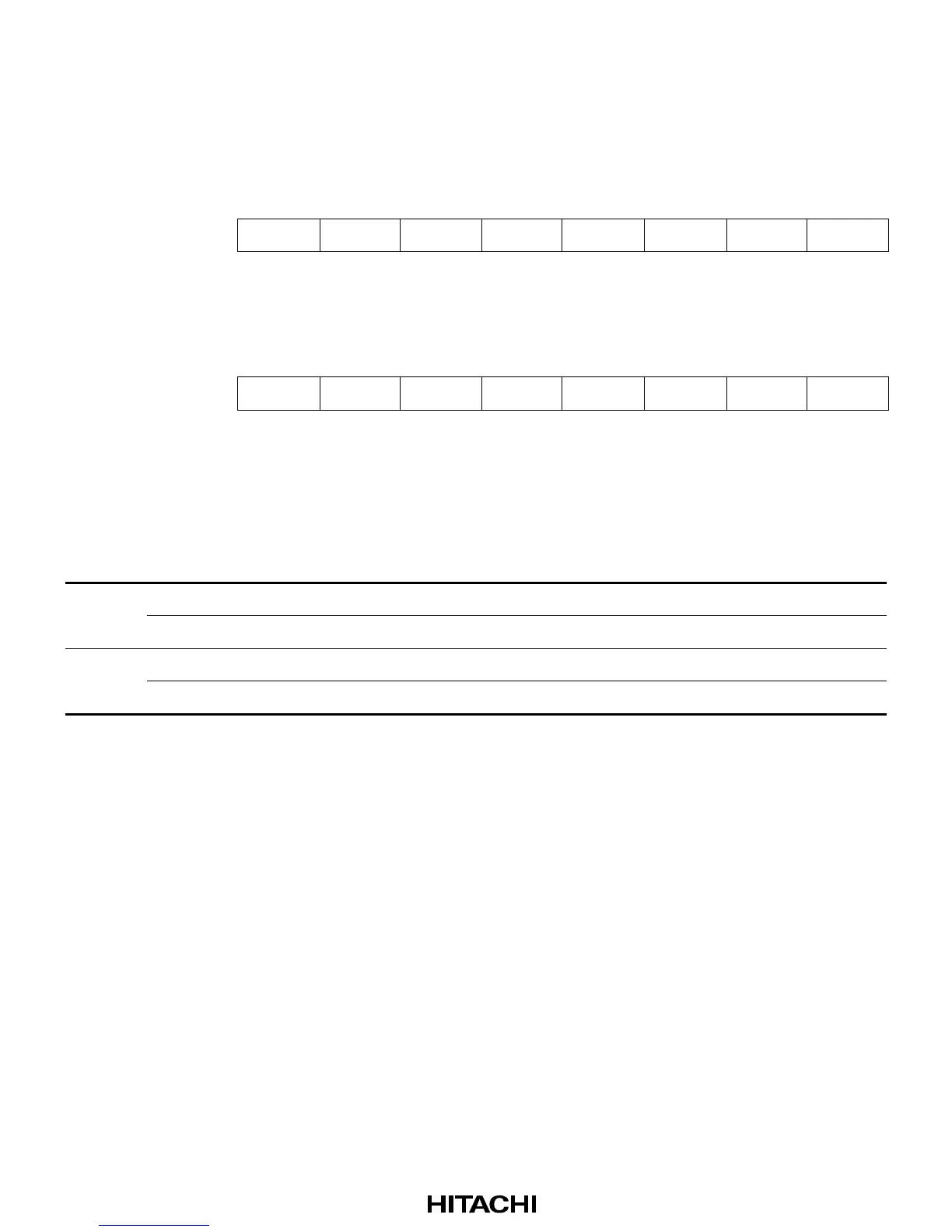

Bit: 7 6 5 4 3 2 1 0

Bit name: PA7DR PA6DR PA5DR PA4DR PA3DR PA2DR PA1DR PA0DR

Initial value: 0 0 0 0 0 0 0 0

R/W: R/W R/W R/W R/W R/W R/W R/W R/W

Table A.55 PADR Bit Functions

PAIOR Pin Function Read Write

0 General input Pin status Can write to PADR, but this does not affect pin status

All other Pin status Can write to PADR, but this does not affect pin status

1 General input PADR value Value written is output from pin

All other PADR value Can write to PADR, but this does not affect pin status

Loading...

Loading...