Philips Semiconductors Product specification

80C31/80C32

80C51 8-bit microcontroller family

128/256 byte RAM ROMless low voltage (2.7V–5.5V),

low power, high speed (33 MHz)

2

2000 Aug 07 853–2213 24293

DESCRIPTION

The Philips 80C31/32 is a high-performance static 80C51 design

fabricated with Philips high-density CMOS technology with operation

from 2.7 V to 5.5 V.

The 80C31/32 ROMless devices contain a 128 × 8 RAM/256 × 8

RAM, 32 I/O lines, three 16-bit counter/timers, a six-source,

four-priority level nested interrupt structure, a serial I/O port for

either multi-processor communications, I/O expansion or full duplex

UART, and on-chip oscillator and clock circuits.

In addition, the device is a low power static design which offers a

wide range of operating frequencies down to zero. Two software

selectable modes of power reduction—idle mode and power-down

mode are available. The idle mode freezes the CPU while allowing

the RAM, timers, serial port, and interrupt system to continue

functioning. The power-down mode saves the RAM contents but

freezes the oscillator, causing all other chip functions to be

inoperative. Since the design is static, the clock can be stopped

without loss of user data and then the execution resumed from the

point the clock was stopped.

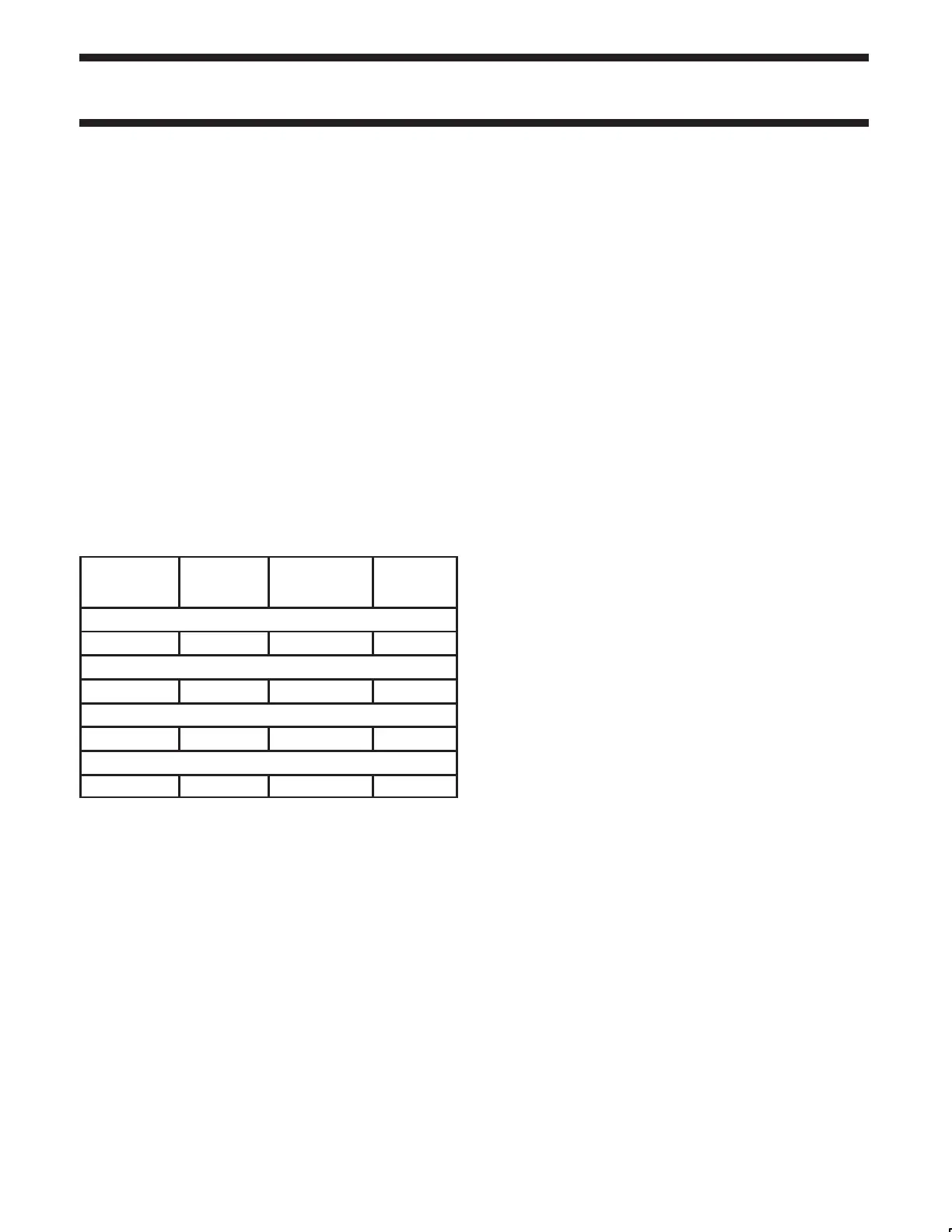

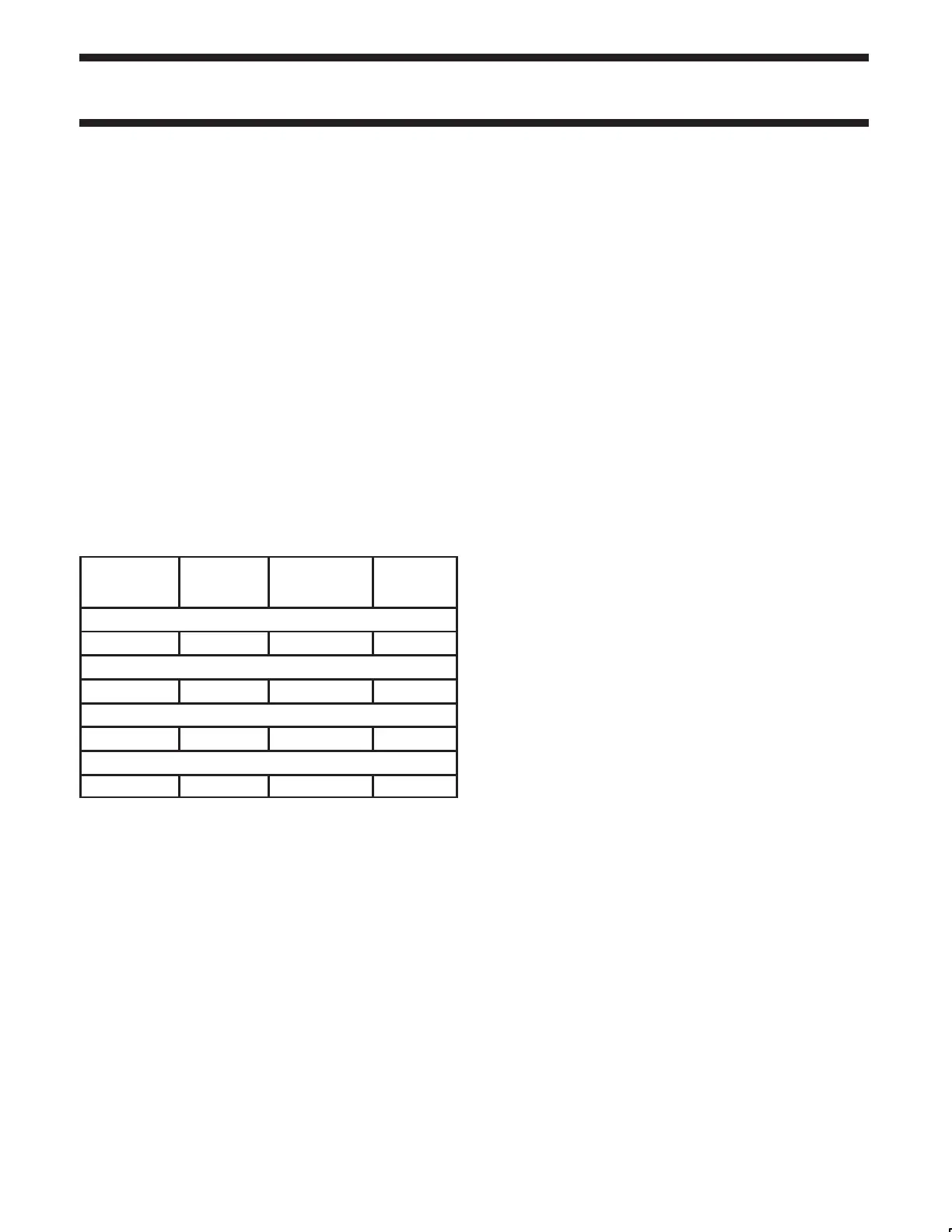

SELECTION TABLE

For applications requiring more ROM and RAM, see the 8XC54/58

and 8XC51RA+/RB+/RC+/80C51RA+ data sheet.

ROM/EPROM

Memory Size

(X by 8)

RAM Size

(X by 8)

Programmable

Timer Counter

(PCA)

Hardware

Watch Dog

Timer

80C31/8XC51

0K/4K 128 No No

80C32/8XC52/54/58

0K/8K/16K/32K 256 No No

80C51RA+/8XC51RA+/RB+/RC+

0K/8K/16K/32K 512 Yes Yes

8XC51RD+

64K 1024 Yes Yes

FEATURES

• 8051 Central Processing Unit

– 128 × 8 RAM (80C31)

– 256 × 8 RAM (80C32)

– Three 16-bit counter/timers

– Boolean processor

– Full static operation

– Low voltage (2.7 V to 5.5 V@ 16 MHz) operation

• Memory addressing capability

– 64k ROM and 64k RAM

• Power control modes:

– Clock can be stopped and resumed

– Idle mode

– Power-down mode

• CMOS and TTL compatible

• TWO speed ranges at V

CC

= 5 V

– 0 to 16 MHz

– 0 to 33 MHz

• Three package styles

• Extended temperature ranges

• Dual Data Pointers

• 4 level priority interrupt

• 6 interrupt sources

• Four 8-bit I/O ports

• Full–duplex enhanced UART

– Framing error detection

– Automatic address recognition

• Programmable clock out

• Asynchronous port reset

• Low EMI (inhibit ALE)

• Wake-up from Power Down by an external interrupt

Loading...

Loading...