3/24/97 3-6 XA Memory Organization

3.4.3 Use and Read/Write Access

Data memory is defined as read-write, and is intended to contain read/write data. It is logically

impossible to execute instructions from XA Data Memory. It is possible, and a common practice,

to add logic to overlap external code and data memory spaces. In this case it is important to

understand that the memory spaces are logically separate. In such a modified Harvard

architecture, implemented with external logic, it is possible –but not recommended– to write

self-modifying XA code. No such overlap is possible for internal data memory.

3.4.4 Data Memory Addressing

XA data memory addressing is optimized for the needs of embedded processing. Data memory

in the XA is divided into 64K byte segments. This provides an intrinsic protection mechanism

for multitasking applications and improves performance by requiring fewer address bits for

localized accesses.

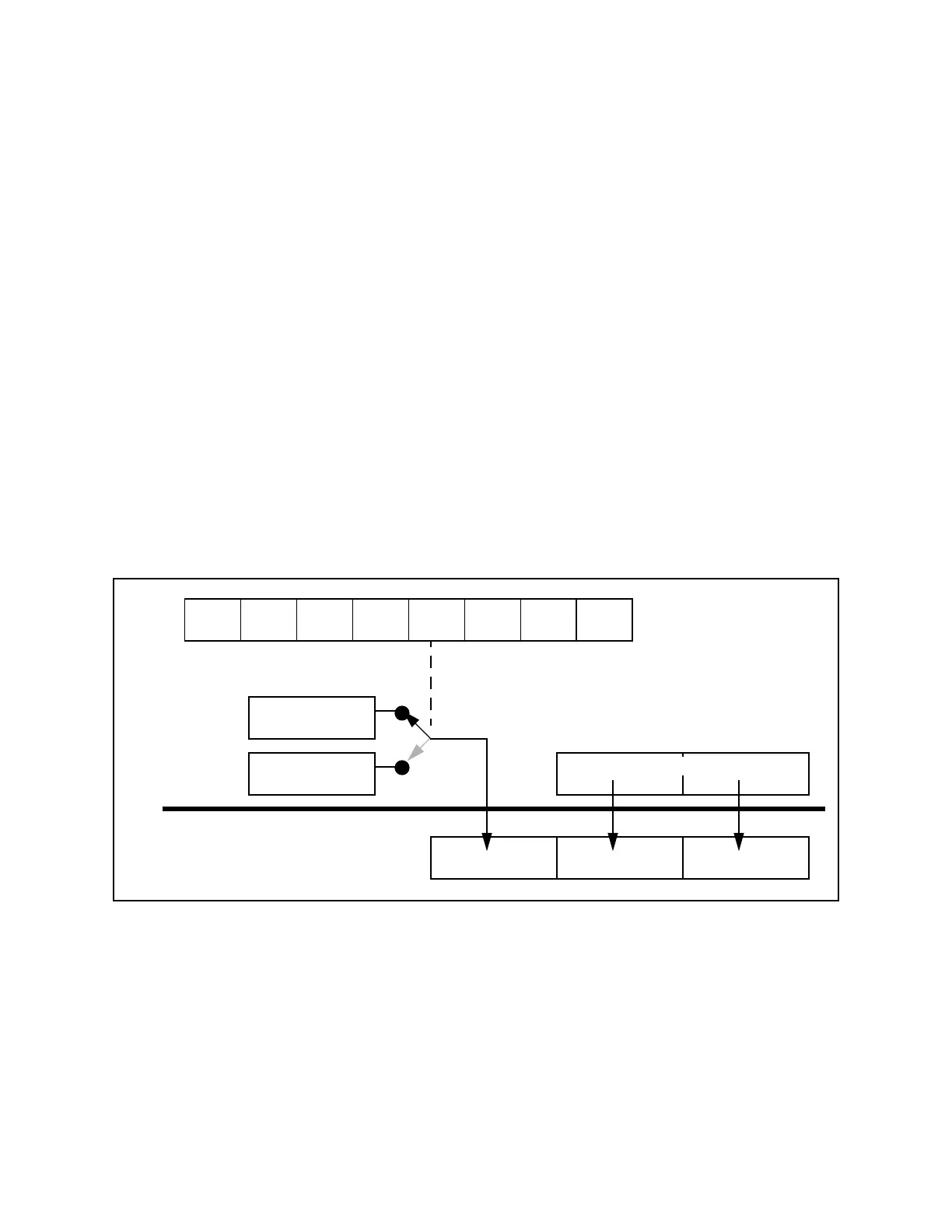

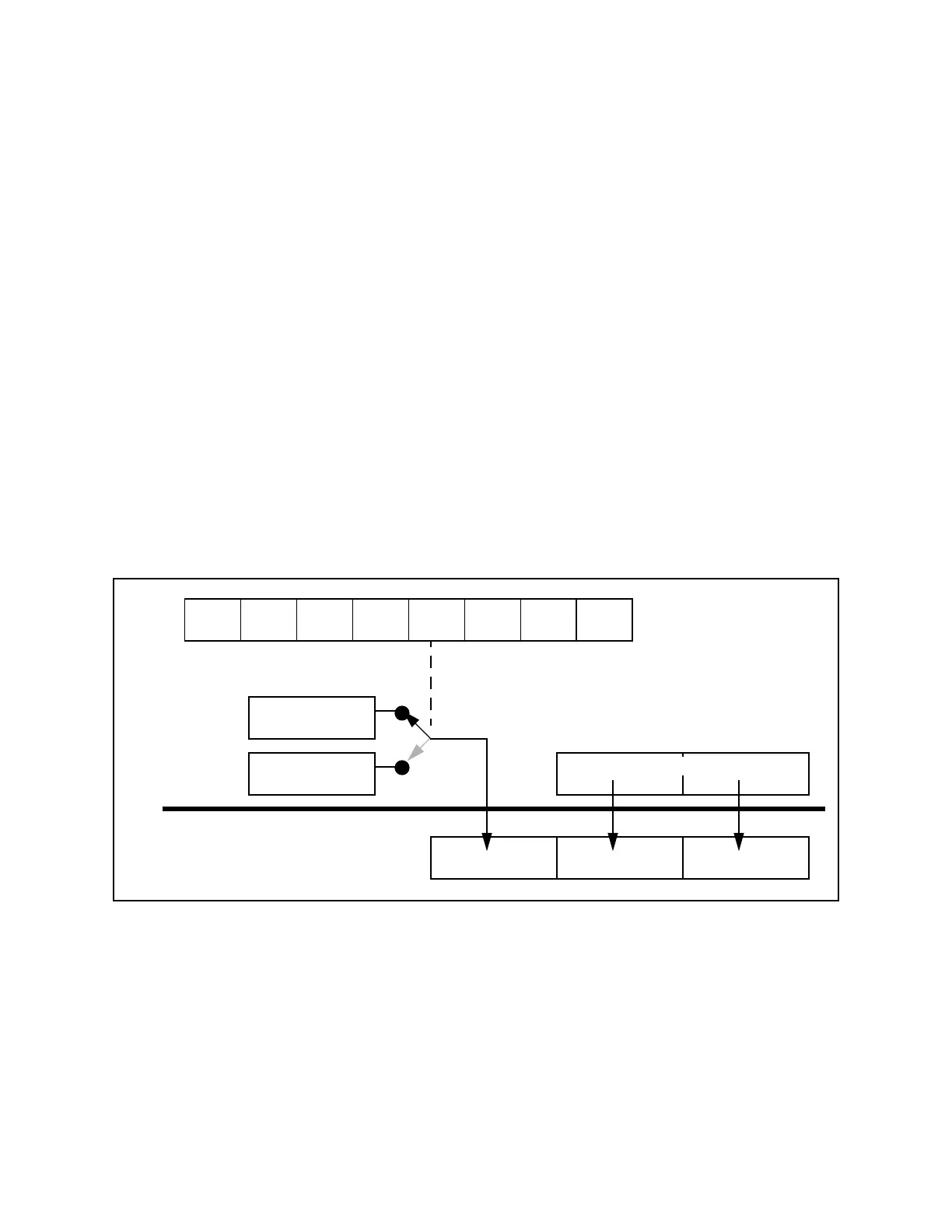

Addressing through Segment Registers

Segment registers provide the upper 8 address bits needed to obtain a complete 24-bit address in

applications that require full use of the XA 16 Mbyte address space. Two segment registers are

defined in the XA architecture for use in accessing data memory, the Data Segment Register

(DS), and the Extra Segment Register (ES). As user stacks are located in the segment specified

by DS, it is probably most convenient to address user data structures through ES. Each pointer

register, namely R0 through R6, is associated with one of the segment registers via the Segment

Select (SSEL) register as illustrated in Figure 3.5.

A 0 in the SSEL bit corresponding to the pointer register selects DS (default on RESET) and 1

selects the ES. For example, when R3 contains a pointer value, the full 24 bit address is formed

by concatenating DS or ES, as determined by the state of SSEL bit 3, as the most significant

8 bits. As a consequence of segmented addressing, the XA data memory space may be viewed as

256 segments of 64K bytes each (Figure 3.6).

Figure 3.5 Address generation

SSEL

ESWEN

R6SEG R5SEG R4SEG R3SEG R2SEG R1SEG

DS

ES R3

complete

24-bit memory

address

segment

registers

8-bit segment

identifier

16-bit segment offset

0

1

R0SEG

Loading...

Loading...