3/24/97 3-8 XA Memory Organization

Bit-level. Bit-level addresses are absolute references to specific bits.

Data move instructions and some special purpose instructions also have additional data

addressing modes as described in Chapter 6.

Indirect Addressing

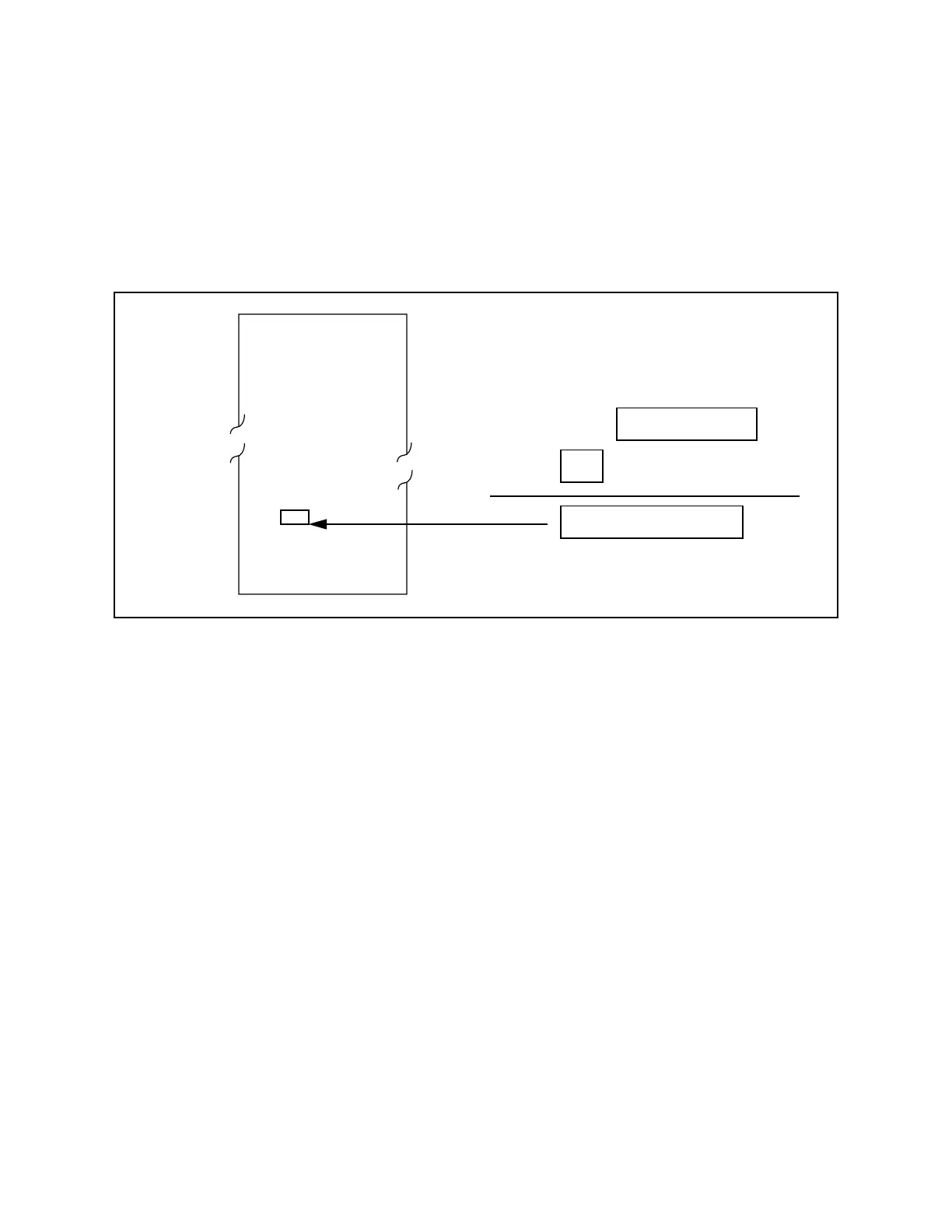

The entire 16 MByte address space is accessible via register-indirect addressing with a segment

register, as illustrated by Figure 3.7 (Note that for simplicity, this figure omits showing how the

Extra Segment or Data Segment Register is chosen using SSEL.).

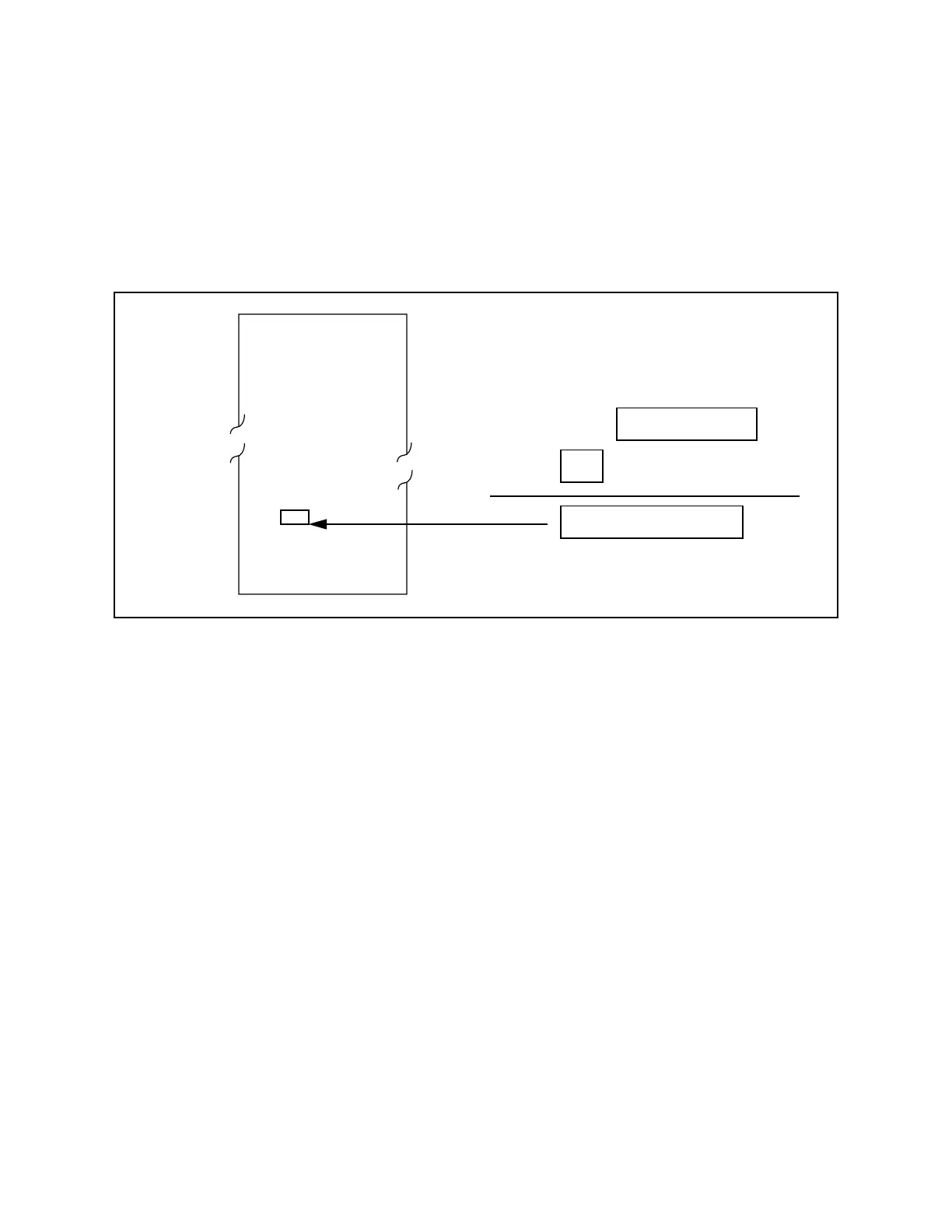

Indirect addressing with an offset is a variant of general indirect addressing in which an 8-bit or

16-bit signed offset contained within the instruction is added to the contents of a pointer register,

then concatenated with an 8-bit segment register to produce a complete address. This mode gives

access to data structures when a pointer register contains the starting address of the structure. It

also supports stack-based parameter passing.

Indirect addressing with autoincrement is another variant of indirect addressing in which the

pointer register contents are automatically incremented following the operation. When the

operand is a byte, the increment is one; when the operand is a word, the increment is 2. Using

indirect addressing with auto-increment provides a convenient method of traversing data

structures smaller than 64K bytes. For data structures exceeding 64K bytes in length, the

program code must explicitly adjust the segment register at page boundaries.

Address generation in these two modes of indirect addressing is illustrated inFigures 3.8 and 3.9.

When using indirect addressing care is necessary to avoid accessing a word quantity at an odd

address. This will result in an access using the next-lower even address, which is generally not

desirable. Note that the indirect addressing with an offset will be successful in this case as long

as the final, effective address is even. That is, both the base address and the offset may be odd.

Figure 3.7 Indirect Access to 24 Bit Address Space

0

FFFFFFh

Rn

16 bits

Seg

Reg

+

8 bits

24 bit address

Loading...

Loading...