3/24/97 4-21 CPU Organization

Note that, like all other forms of interrupts, the PSW (including the Interrupt Mask bits) is loaded

from the interrupt vector table when an event interrupt is serviced. Thus, the priority at which the

interrupt service routine executes could be different than the priority at which the interrupt

occurred (since that was determined not by the PSW image in the vector table, but by the

Interrupt Priority register setting for that interrupt). Normally, it is advisable to set the execution

priority in the interrupt vector to be the same as the Interrupt Priority register setting that will be

used in the program.

Furthermore, the occurrence priority of an interrupt should never be set higher than the execution

priority. This could lead to infinite interrupt nesting where the interrupt service routine is re-

interrupted immediately upon entry by the same interrupt source.

Software Interrupts

Software Interrupts act just like event interrupts, except that they are caused by software writing

to an interrupt request bit in an SFR. The standard implementation of the software interrupt

mechanism provides 7 interrupts which are associated with 2 Special Function Registers. One

SFR, the software interrupt request register (SWR), contains 7 request bits: one for each software

interrupt. The second SFR is an enable register (SWE), containing one enable bit matching each

software interrupt request bit.

Software interrupts are initiated by setting one of the request bits in the SWR register. If the

corresponding enable bit in the SWE register is also set, the software interrupt will occur when it

becomes the highest priority pending interrupt and its priority is higher than the current

execution level. The software interrupt request bit in SWR must be cleared by software prior to

returning from the software interrupt service routine.

Software interrupts have fixed interrupt priorities, one each at priorities 1 through 7. These are

shown in Table 4.2 below. Software Interrupts are defined outside the XA core and may not be

present on all XA derivatives; consult the specific XA derivative data sheet for details.

The primary purpose of the software interrupt mechanism is to provide an organized way in

which portions of event interrupt routines may be executed at a lower priority level than the one

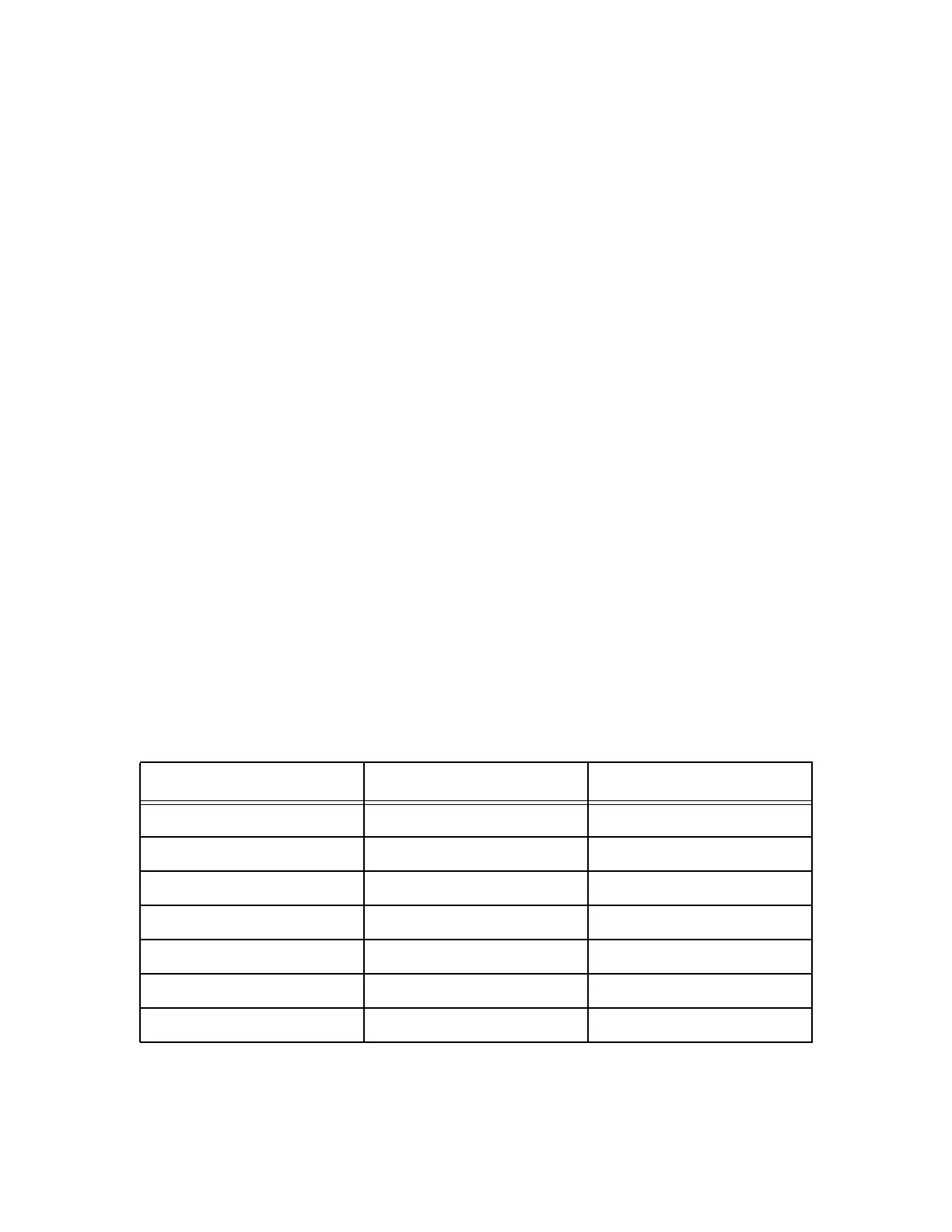

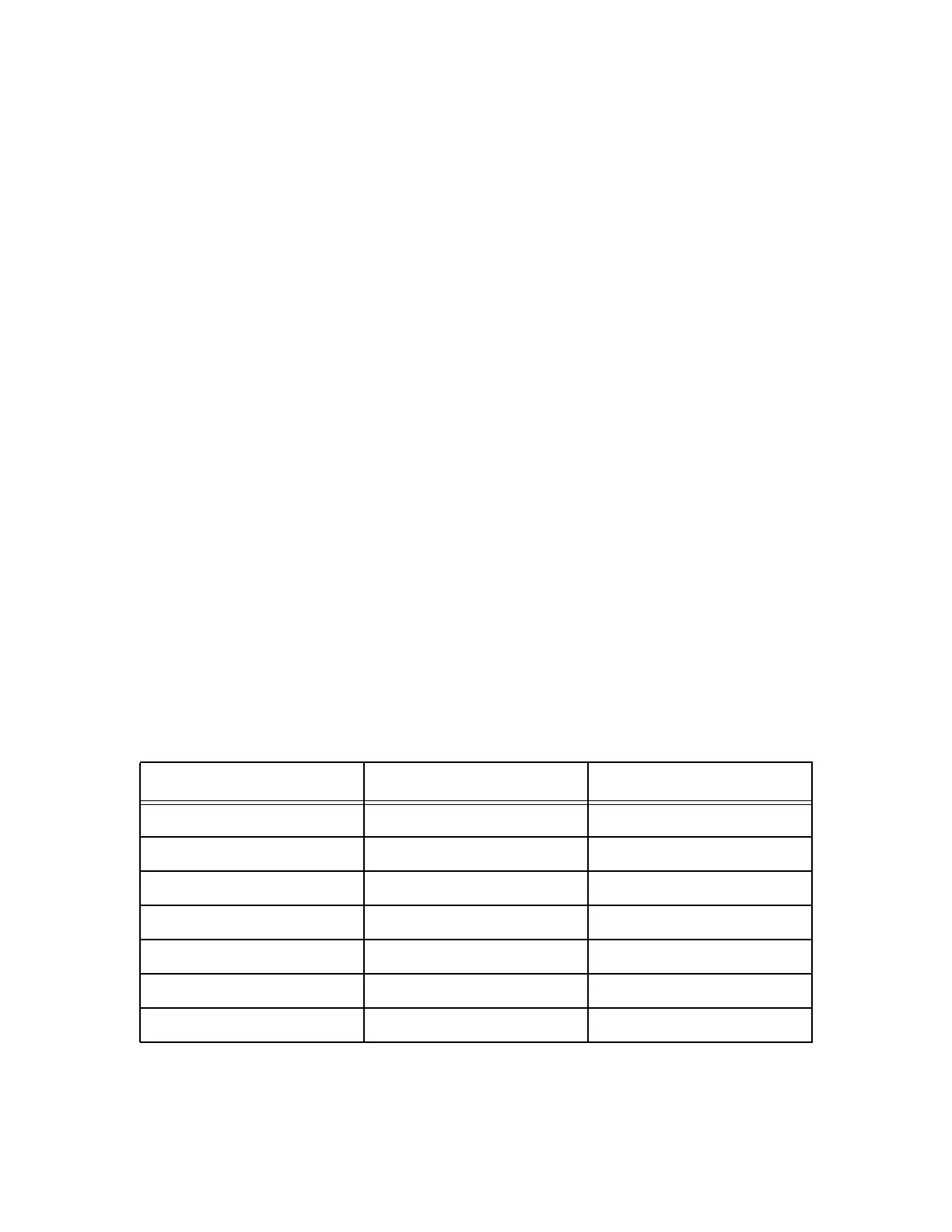

Table 4.2: Software interrupts, vectors, and fixed priorities

Software Interrupt Vector Address Fixed Priority

SWI1 0100h:0103h 1

SWI2 0104h:0107h 2

SWI3 0108h:010Bh 3

SWI4 010Ch:010Fh 4

SWI5 0110h:0113h 5

SWI6 0114h:0117h 6

SWI7 0118h:011Bh 7

Loading...

Loading...