XA User Guide 4-22 3/24/97

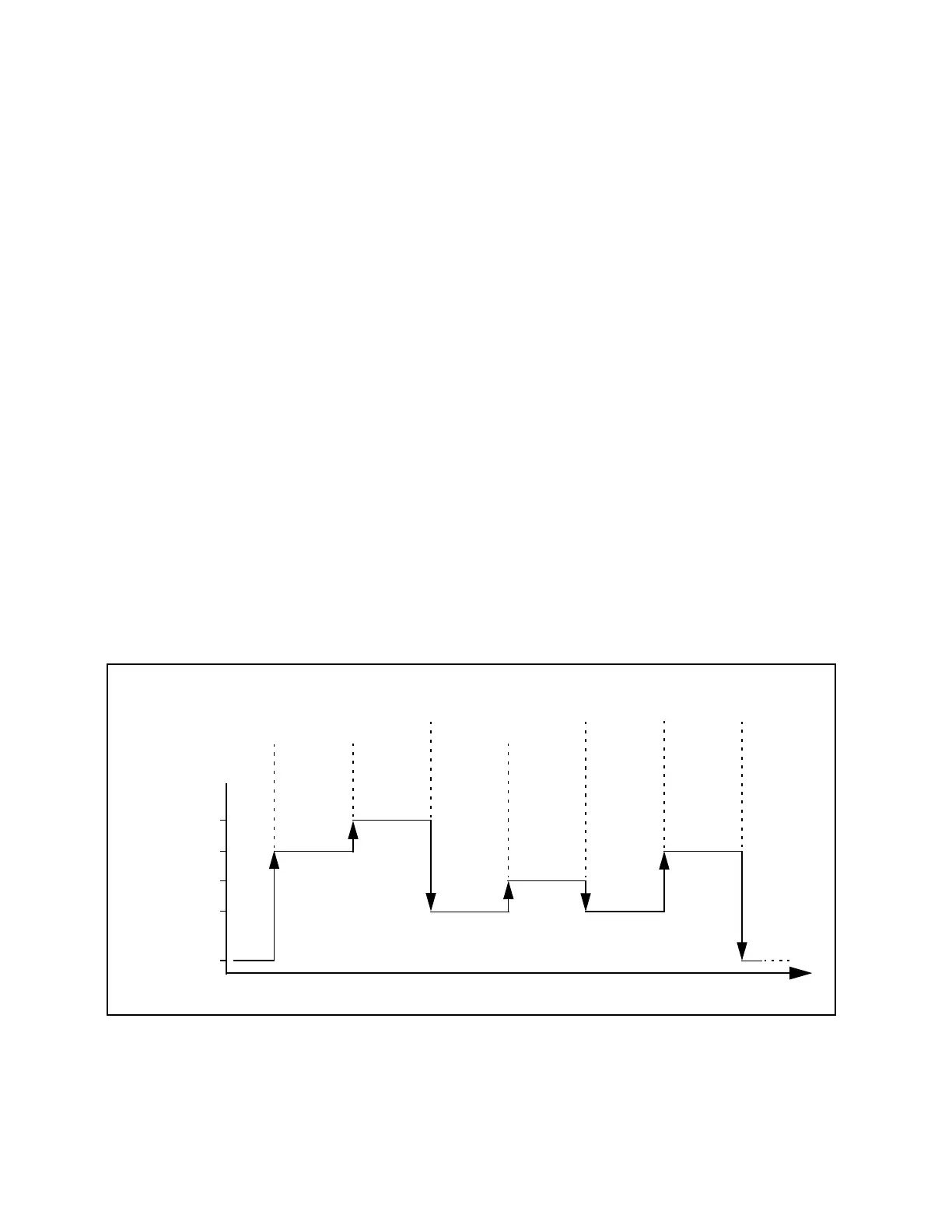

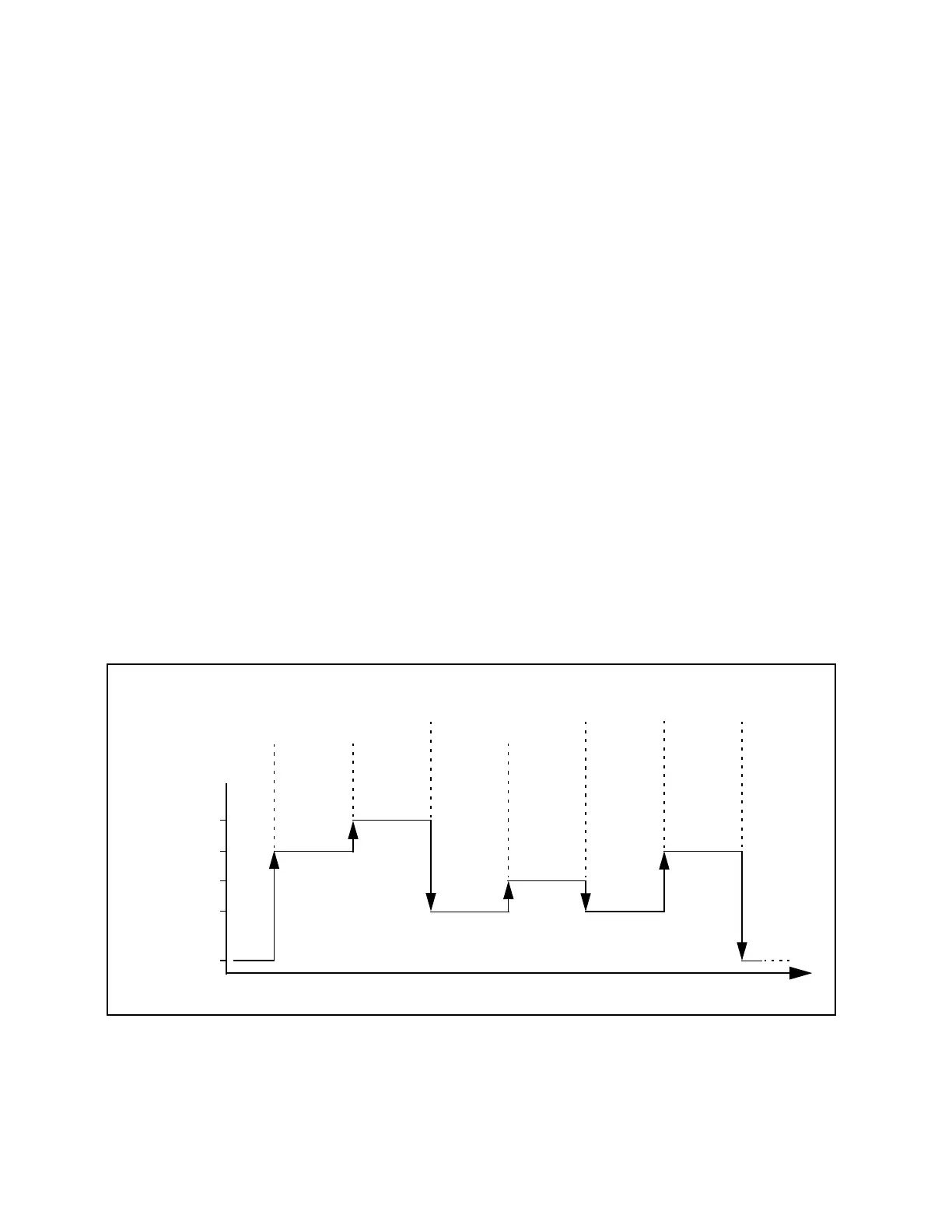

at which the service routine began. An example of this would be an event Interrupt Service

Routine that has been given a very high priority in order to respond quickly to some critical

external event. This ISR has a relatively small portion of code that must be executed

immediately, and a larger portion of follow-up or “clean-up” code which does not need to be

completed right away. Overall system performance may be improved if the lower priority portion

of the ISR is actually executed at a lower priority level, allowing other more important interrupts

to be serviced.

If the high priority ISR simply lowers its execution priority at the point where it enters the

follow-up code, by writing a lower value to the IM bits in the PSW, a situation called “priority

inversion” could occur. Priority inversion describes a case where code at a lower priority is

executing while a higher priority routine is kept waiting. An example of how this could occur by

writing to the IM bits follows, and is illustrated in Figure 4.15.

Suppose code is executing at level 0 and is interrupted by an event interrupt that runs at level 10.

This is again interrupted by a level 12 interrupt. The level 12 ISR completes a time-critical

portion of its code and wants to lower the priority of the remainder of its code (the non-time

critical portion) in order to allow more important interrupts to occur. So, it writes to the IM bits,

setting the execution priority to 5. The ISR continues executing at level 5 until a level 8 event

interrupt occurs. The level 8 ISR runs to completion and returns to the level 5 ISR, which also

runs to completion. When the level 5 ISR returns, the previously interrupted level 10 ISR is re-

activated and eventually competes.

It can be seen in this example that lower priority ISR code executed and completed while higher

priority code was kept waiting on the stack. This is priority inversion.

In those cases where it is desirable to alter the priority level of part of an ISR, a software

interrupt may be used to accomplish this without risk of priority inversion. The ISR must first be

Figure 4.15 Example of priority inversion (see text)

Level 12

interrupt

occurs

Level 10

interrupt

occurs

Level 8

interrupt

occurs

Time

Execution

Priority

0

8

10

5

12

Priority

lowered

Return to

level 5

Return to

level 10

Return to

level 0

Loading...

Loading...