3/24/97 4-23 CPU Organization

split into 2 pieces: the high priority portion, and the lower priority portion. The high priority

portion remains associated with the original interrupt vector. The lower priority portion is

associated with the interrupt vector for software interrupt 5. At the completion of the high

priority portion of the ISR, the code sets the request bit for software interrupt 5, then returns. the

remainder of the ISR, now actually the ISR for software interrupt 5, executes when it becomes

the highest priority pending interrupt.

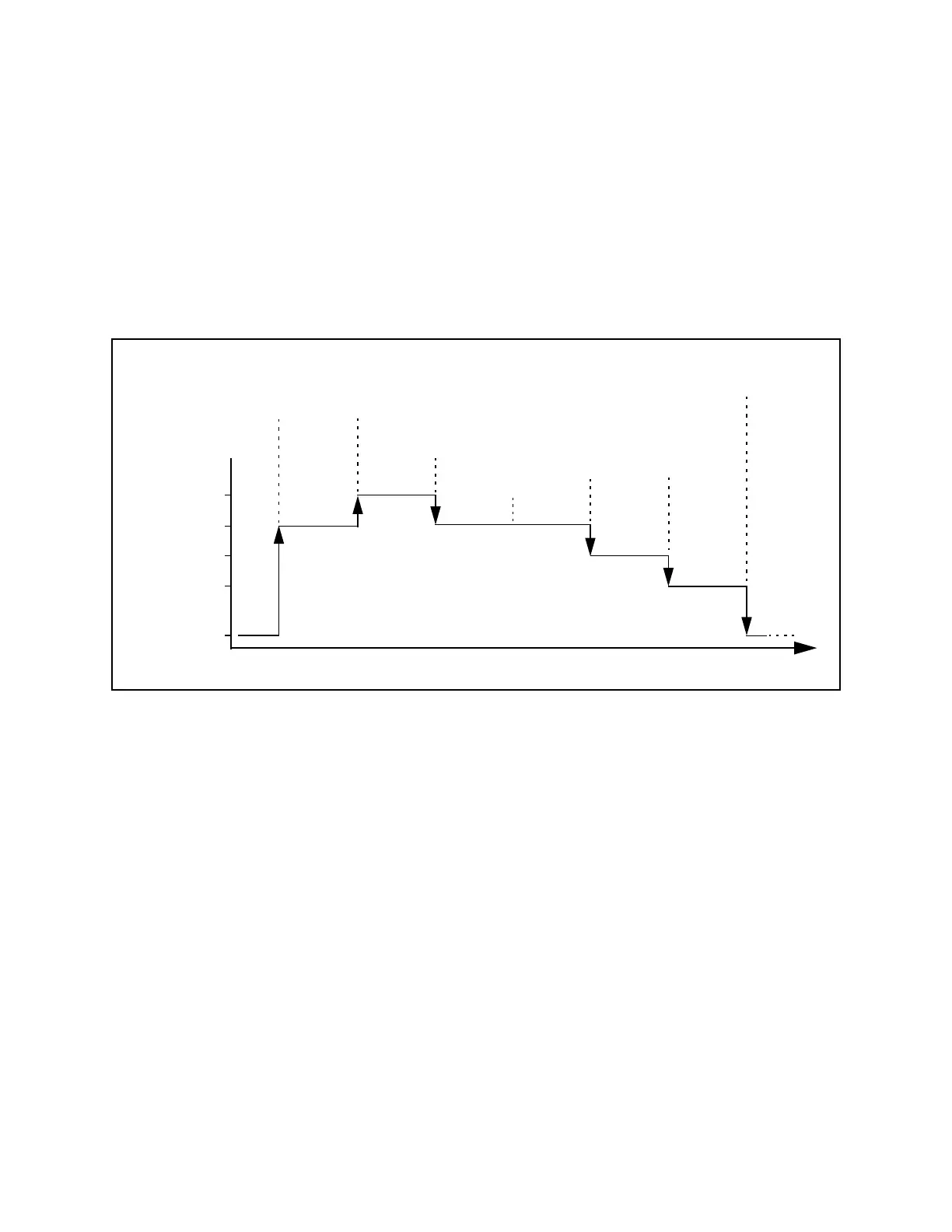

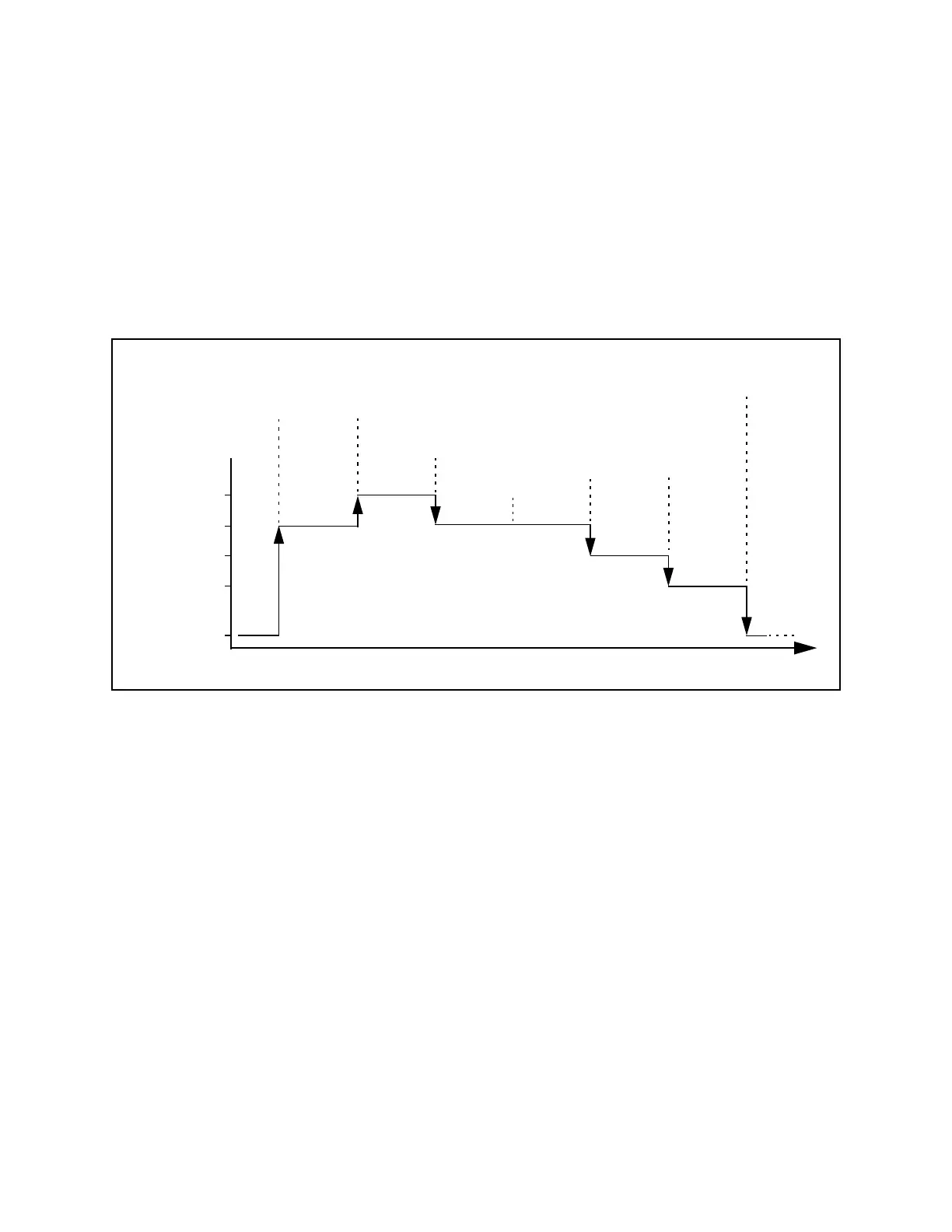

The diagram in Figure 4.16 shows the same sequence of events as in the example of priority

inversion, except using software interrupt 5 as just described. Note that the code now executes in

the correct order (higher priority first).

Trap Interrupts

Trap Interrupts are generated by the TRAP instruction. TRAP 0 through TRAP 15 are defined

and may be used as required by applications. Trap Interrupts are intended to support application-

specific requirements, as a convenient mechanism to enter globally used routines, and to allow

transitions between user mode and system mode. A trap interrupt will occur if and only if the

instruction is executed, so there is no need for a precedence scheme with respect to simultaneous

traps.

The effect of a TRAP is immediate, the corresponding TRAP service routine is entered upon

completion of the TRAP instruction.

See Chapter 6 for a detailed description of the TRAP instruction.

4.8.2 Interrupt Service Data Elements

There are two data elements associated with XA interrupts. The first is the stack frame created

when each interrupt is serviced. The second is the interrupt vector table located at the beginning

Figure 4.16 Example use of software interrupt (see text)

Level 12

interrupt

occurs

Level 10

interrupt

occurs

Level 8

interrupt

occurs,

but waits

for level

10 to

complete

Software

interrupt

5 issued,

return to

level 10

Return

from level

level 10,

level 8

interrupt

serviced

Return to

level 0

Time

Execution

Priority

0

8

10

5

12

Return

from level

8, level 5

software

interrupt

serviced

Loading...

Loading...