2

Introduction

The Intersil 82C59A is a CMOS Priority Interrupt Controller,

designed to relieve the system CPU from the task of polling

in a multi-level priority interrupt system. The 82C59A is

compatible with microprocessors such as the 80C86,

80C88, 8086, 8088, 8080/85 and NSC800.

In the following discussion, we will look at the initialization

and operation process for the 82C59A. We will focus our

attention on 80C86/80C88-based systems. However, the

information presented will also be applicable to use of the

82C59A in 8080 and 8085-based systems as well.

Let us look at the sequence of events that occur with the

82C59A during an interrupt request and service. In an

8080/85 based system:

1. One or more of the INTERRUPT REQUEST lines (IR0 -

IR7) are raised high, setting the corresponding bits in the

Interrupt Request Register (IRR).

2. The interrupt is evaluated in the priority resolver. If appropri-

ate, an interrupt is sent to the CPU via the INT line (pin 17).

3. The CPU acknowledges the interrupt by sending a pulse

on the

INTA line. Upon reception of this pulse, the

82C59A responds by forcing the opcode for a call instruc-

tion (0CDH) onto the data bus.

4. A second

INTA pulse is sent from the CPU. At this time,

the device will respond by placing the lower byte of the

address of the appropriate service routine onto the data

bus. This address is derived from ICW1.

5. A final (third) pulse of

INTA occurs, and the 82C59A re-

sponds by placing the upper byte of the address onto the

data bus. This address is taken from ICW2.

6. The three byte call instruction is then complete. If the

AEOI mode has been chosen, the bit set during the first

INTA pulse in the ISR is reset at the end of the third INTA

pulse. Otherwise, it will not get reset until an appropriate

EOI command is issued to the 82C59A.

For 80C86- and 80C88-based systems:

1. and 2. same as above.

2. The CPU responds to the interrupt request by pulsing the

INTA line twice. The first pulse sets the appropriate ISR

bit and resets the IRR bit while the second pulse causes

the interrupt vector to be placed on the data bus. This

byte is composed of the interrupt number in bits 0 through

2, and bits 3 through 7 are taken from bits 3 - 7 of ICW2.

3. The interrupt sequence is complete. If using the AEOI

mode, the bit set earlier in the ISR will be reset. Other-

wise, the interrupt controller will await an appropriate EOI

command at the end of the interrupt service routine.

1.0 Glossary of Terms for the 82C59A

1.1 Automatic End of Interrupt (AEOI)

When the 82C59A is programmed to operate in the

Automatic EOI mode, the device will produce its own End-of-

Interrupt (EOI) at the trailing edge of the last Interrupt

Acknowledge pulse (

INTA) from the CPU. Using this mode of

operation frees the software (service routines) from needing

to send an EOI manually to the 82C59A.

However, using the Automatic EOI mode will upset the

priority structure of the 82C59A. When the AEOI is

generated, the bit that was set in the In-Service Register

(ISR) to indicate which interrupt is being serviced, will be

cleared. Because of this, while an interrupt is being serviced

there will be no record in the ISR that it is being serviced.

Unless interrupts are disabled by the CPU, there is a risk

that interrupt requests of lower or equal priority will interrupt

the current request being serviced. If this mode of operation

is not desired, interrupts should not be re-enabled by the

CPU when executing interrupt service routines.

1.2 Automatic Rotation

During normal operation of the 82C59A, we have an

assigned order of priorities for the IR lines. There are

however, instances when it might be useful to assign equal

priorities to all interrupts. Once a particular interrupt has

been serviced, all other equal priority interrupts should have

an opportunity to be serviced before the original peripheral

can be serviced again. This priority equalization can be

achieved through Automatic Rotation of priorities.

Assume, for example, that the assigned priorities of interrupts

has IR0 as the highest priority interrupt and IR7 as the lowest.

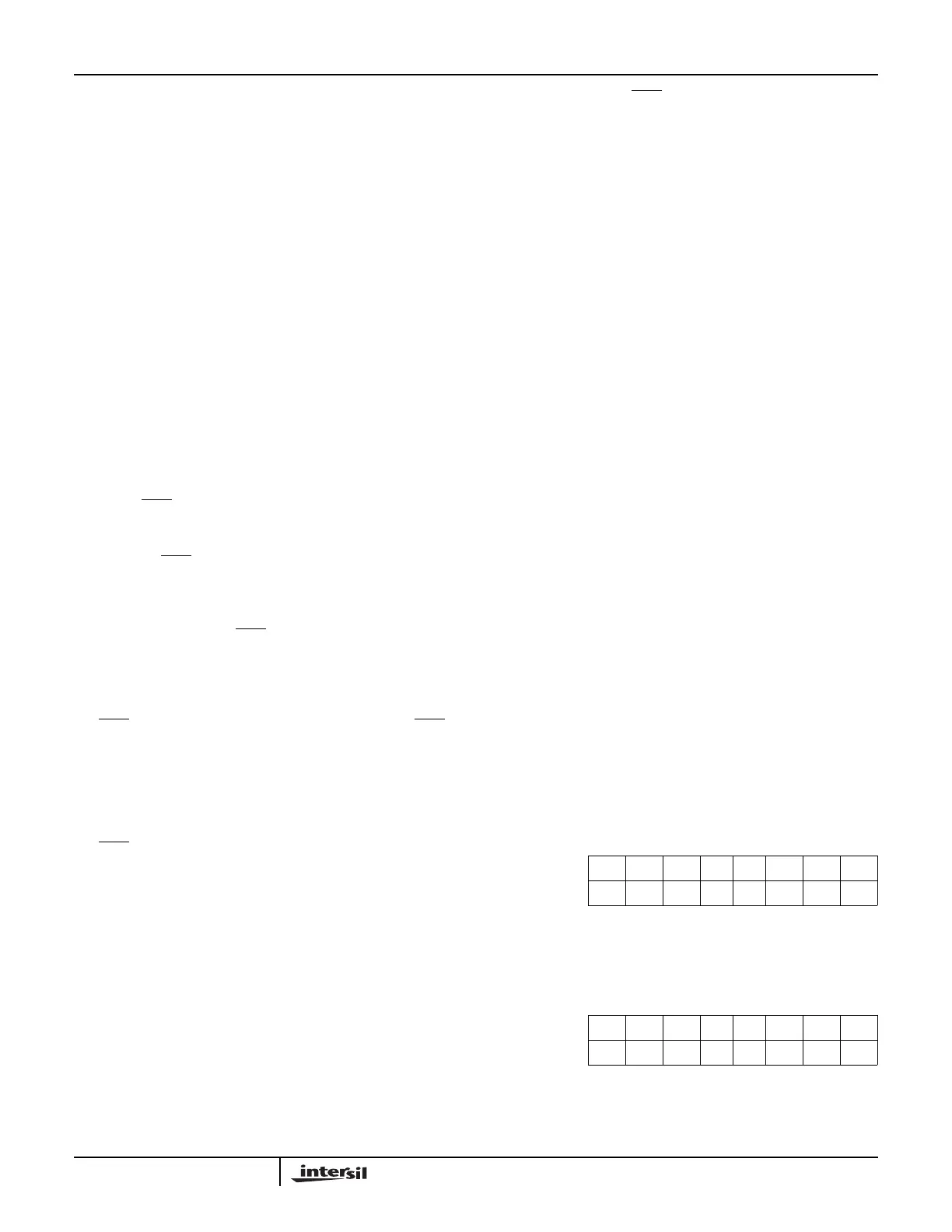

Figure 1A shows interrupt requests occurring on IR7 as well

as IR3. Because IR3 is of higher priority, it will be serviced

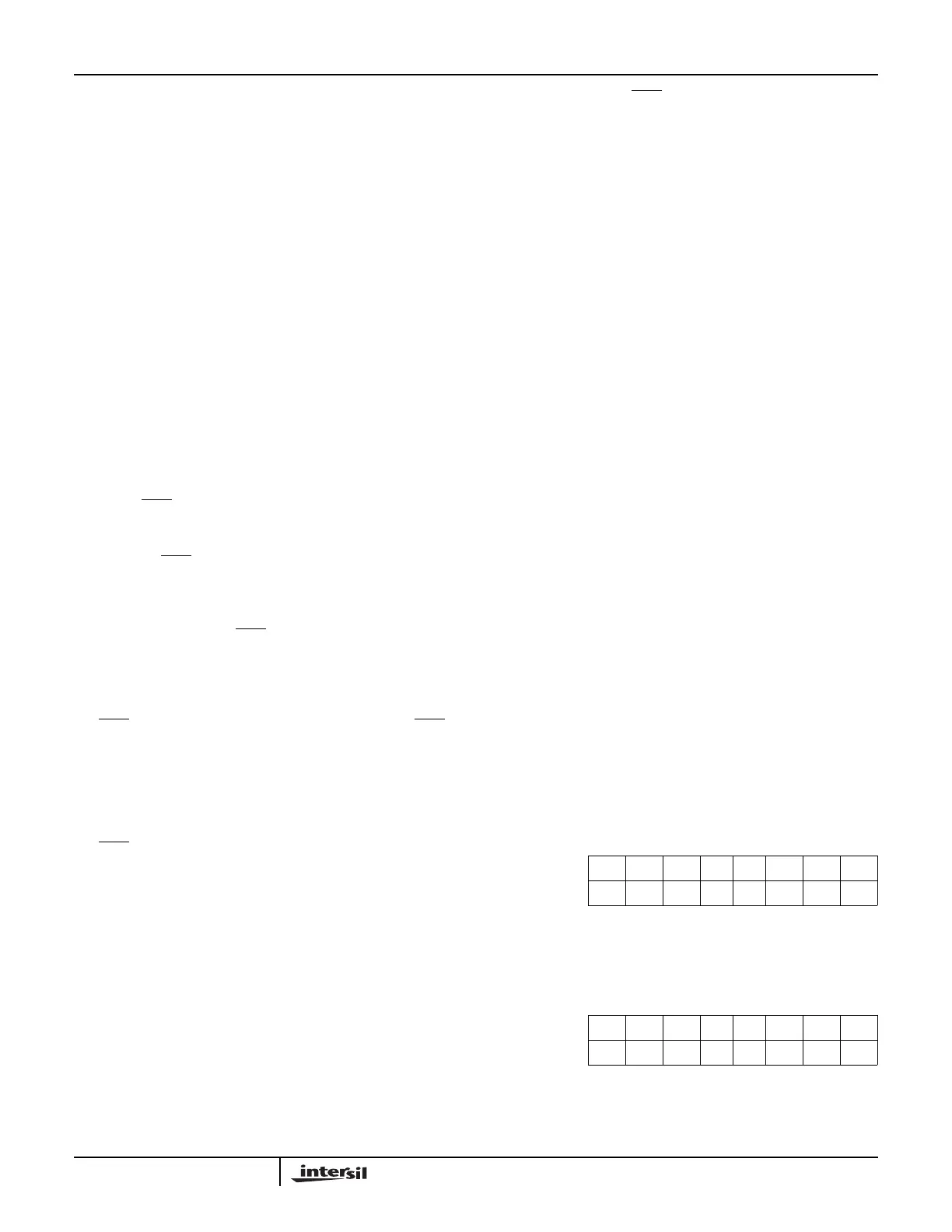

first. Upon completion of the servicing of IR3, rotation occurs

and IR3 then becomes the lowest priority interrupt. IR4 will

now have the highest priority (See Figure 1B).

There are two methods in which Automatic Rotation can be

implemented. First, if the 82C59A is operating in the AEOI

mode as described above, the 82C59A can be programmed

for “Rotate in Automatic EOI mode”. This is done by writing a

command word to OCW2. The second method occurs when

using normal EOIs. When an EOI is issued by the service

routine, the software can specify that rotation be performed.

IR7 IR6 IR5 IR4 IR3 IR2 IR1 IR0

IRR STATUS 1 0 0 0 1 0 0 0

PRIORITY 7 6 5 4 3 2 1 0

LOWEST

PRIORITY

HIGHEST

PRIORITY

FIGURE 1A. IR PRIORITIES (BEFORE ROTATION)

IR7 IR6 IR5 IR4 IR3 IR2 IR1 IR0

IRR STATUS 1 0 0 0 0 0 0 0

PRIORITY 3 2 1 0 7 6 5 4

HIGHEST

PRIORITY

LOWEST

PRIORITY

FIGURE 1B. IR PRIORITIES (AFTER ROTATION)

Application Note 109

Loading...

Loading...