XA User Guide 3-9 3/24/97

Direct Addressing

The first 1K of each segment is directly addressable. Address generation for the direct address

mode is summarized in Figure 3.10. Segment register DS is always used.

Direct data-reference instructions encode a maximum of 10 address bits, which are zero extended

to sixteen bits and concatenated with DS to form an absolute 24 bit address. In all segments, direct

addressing can be used to access any byte in the first 1K bytes of the segment.

SFR Addressing

A 1K portion of the direct address space, addresses 400h through 7FFh, is reserved for SFR

addresses. The SFR address space uses a portion of the direct address space, but represents a

completely distinct logical area that is not related to the data memory segmentation scheme. See

section 3.6 for a complete description of SFR access.

Bit Addressing

Thirty-two bytes of each segment of data memory are also bit-addressable, starting at offset 20h

in the segment addressed by the DS register. Address generation for bit addressing in the data

memory space is shown in Figure 3.10. As described in chapter 6, bits are encoded in

instructions as 10 bits. Figure 3.11 shows the bit addresses as they appear in memory .

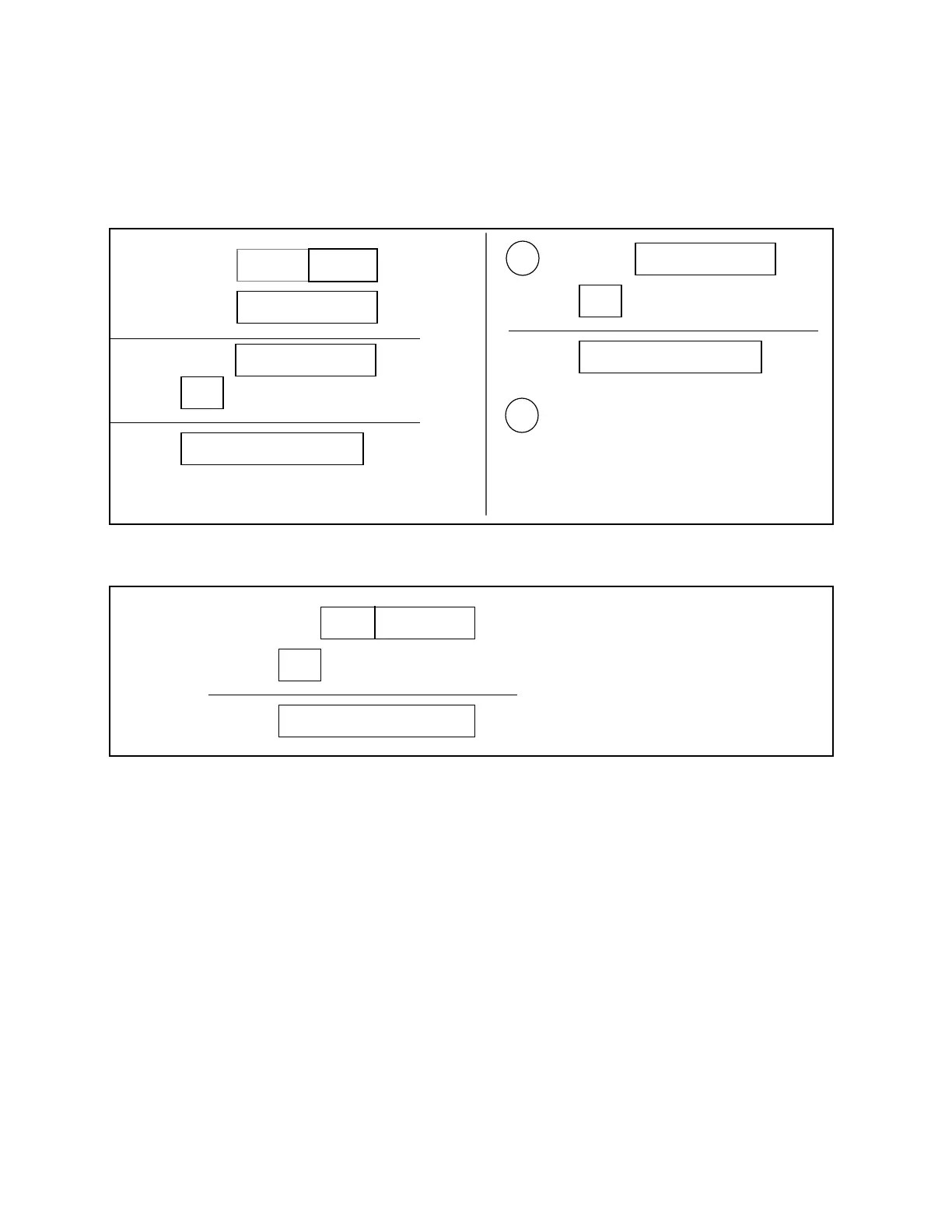

Figure 3.8 Indirect Addressing

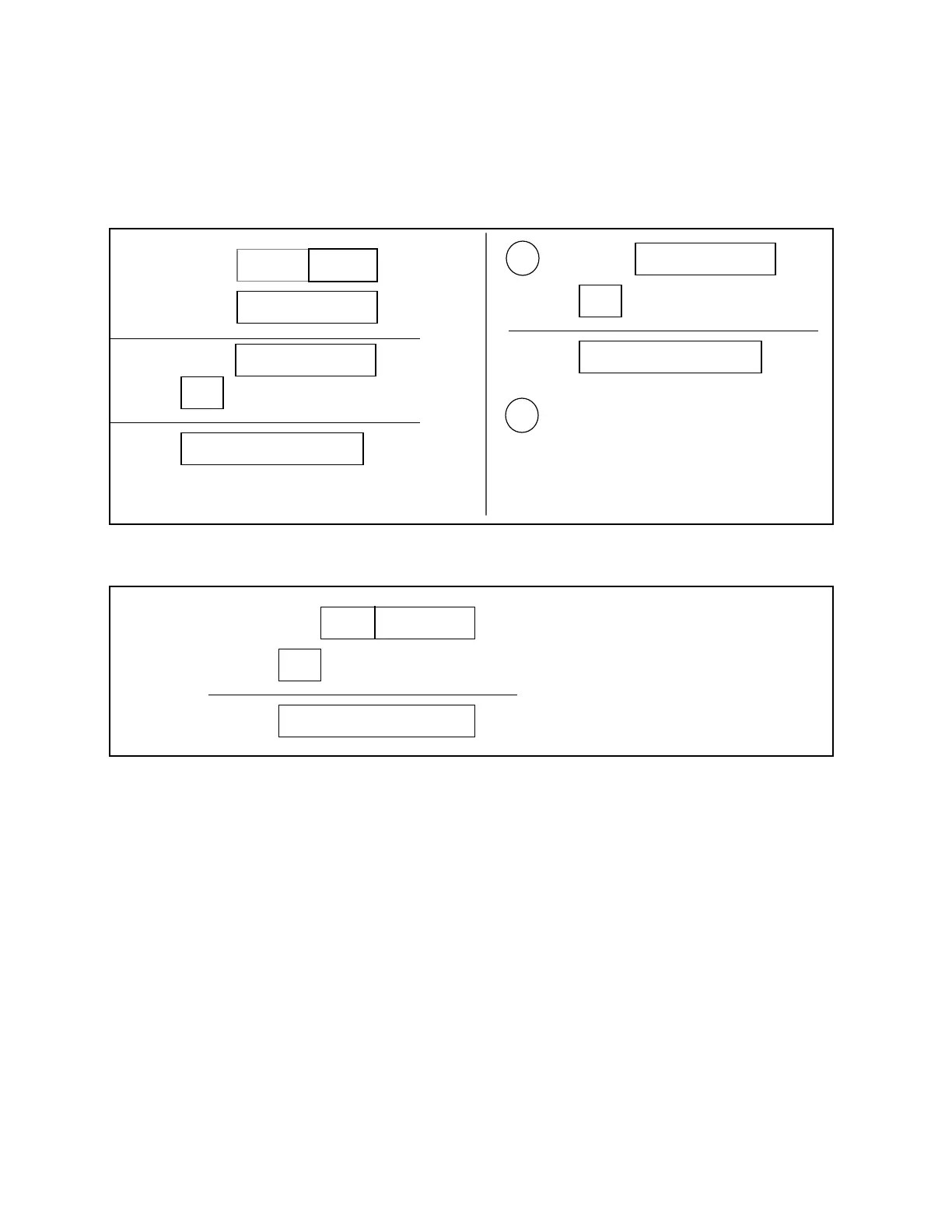

Figure 3.9 Direct address generation

Rn

16 bits

Seg

Reg

+

8 bits

24 bit address

a) Indirect addressing with offset b) indirect addressing with auto increment

8 or 16-bit

signed offset

+

partial

indirect addr

Rn

16 bits

Seg

Reg

+

8 bits

24 bit address

1

2

Rn <-- Rn + data size

Direct address from instruction

10 bits

DS (data segment register)

+

8 bits

24 bit address

0

Loading...

Loading...