Intel387

TM

SX MATH COPROCESSOR

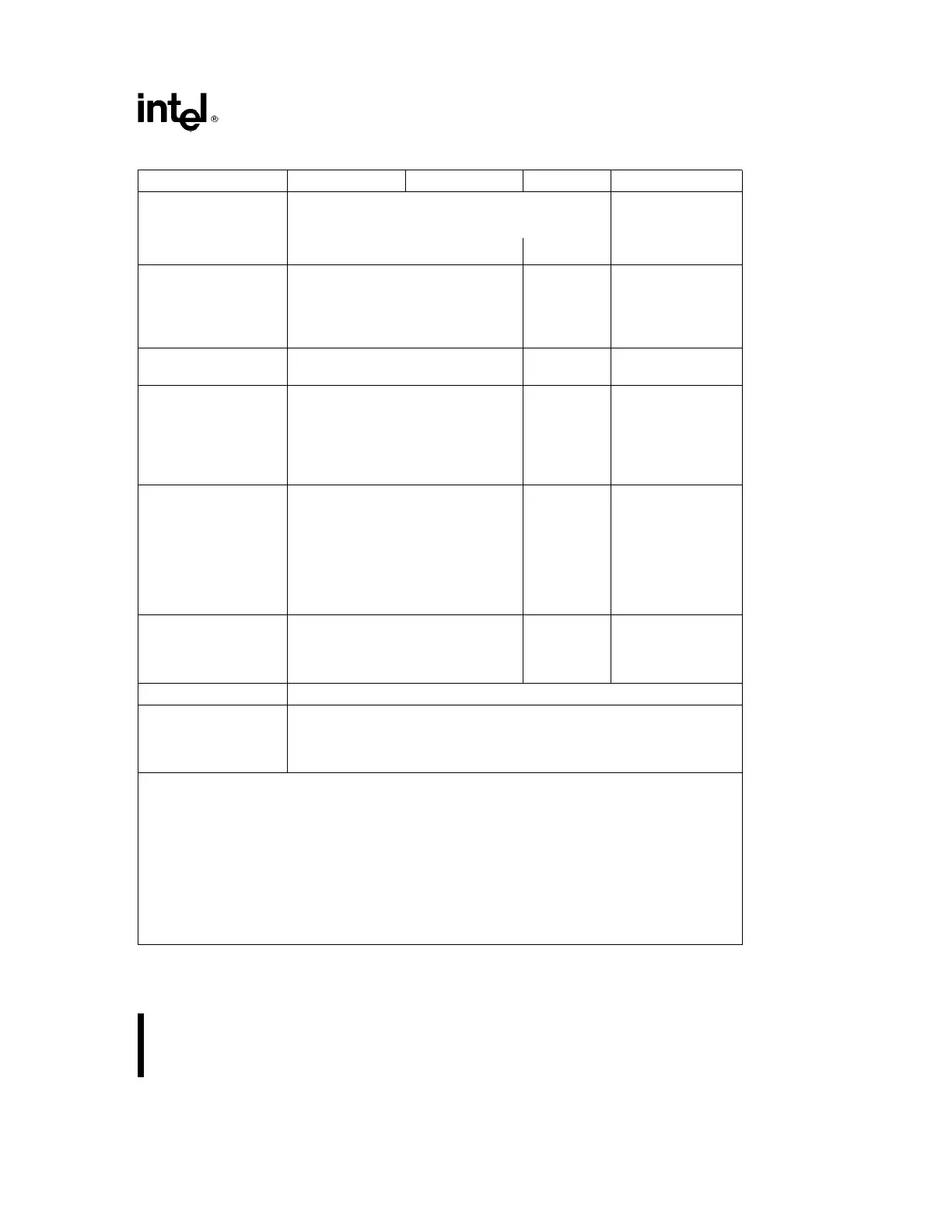

Table 3-1. Condition Code Interpretation

Instruction C0 (S) C3 (Z) C1 (A) C2 (C)

FPREM, FPREM1 Three least significant bits

Reduction

(see Table 3-2) of quotient

0

e

complete

Q2 Q0 Q1

1

e

incomplete

or O/U

Ý

FCOM, FCOMP,

FCOMPP, FTST, Result of comparison

Zero

Operand is not

FUCOM, FUCOMP, (see Table 3-3)

or O/U

Ý

comparable

FUCOMPP, FICOM, (Table 3-3)

FICOMP

FXAM Operand class Sign Operand class

(see Table 3-4) or O/U

Ý

(Table 3-4)

FCHS, FABS, FXCH,

FINCSTP, FDECSTP,

Zero

Constant loads, UNDEFINED UNDEFINED

FXTRACT, FLD,

or O/U

Ý

FILD, FBLD,

FSTP (ext real)

FIST, FBSTP,

FRNDINT, FST,

FSTP, FADD, FMUL,

Roundup

FDIV, FDIVR, UNDEFINED UNDEFINED

FSUB, FSUBR,

or O/U

Ý

FSCALE, FSQRT,

FPATAN, F2XM1,

FYL2X, FYL2XP1

FPTAN, FSIN Roundup Reduction

FCOS, FSINCOS UNDEFINED or O/U

Ý

,0

e

complete

undefined 1

e

incomplete

if C2

e

1

FLDENV, FRSTOR Each bit loaded from memory

FLDCW, FSTENV,

FSTCW, FSTSW, UNDEFINED

FCLEX, FINIT,

FSAVE

O/U

Ý

When both IE and SF bits of status word are set, indicating a stack exception, this bit

distinguishes between stack overflow (C1

e

1) and underflow (C1

e

0).

Reduction If FPREM or FPREM1 produces a remainder that is less than the modulus, reduction is

complete. When reduction is incomplete the value at the top of the stack is a partial

remainder, which can be used as input to further reduction. For FPTAN, FSIN, FCOS, and

FSINCOS, the reduction bit is set if the operand at the top of the stack is too large. In this

case the original operand remains at the top of the stack.

Roundup When the PE bit of the status word is set, this bit indicates whether the last rounding in the

instruction was upward.

UNDEFINED Do not rely on finding any specific value in these bits.

13

13

Loading...

Loading...