Intel387

TM

SX MATH COPROCESSOR

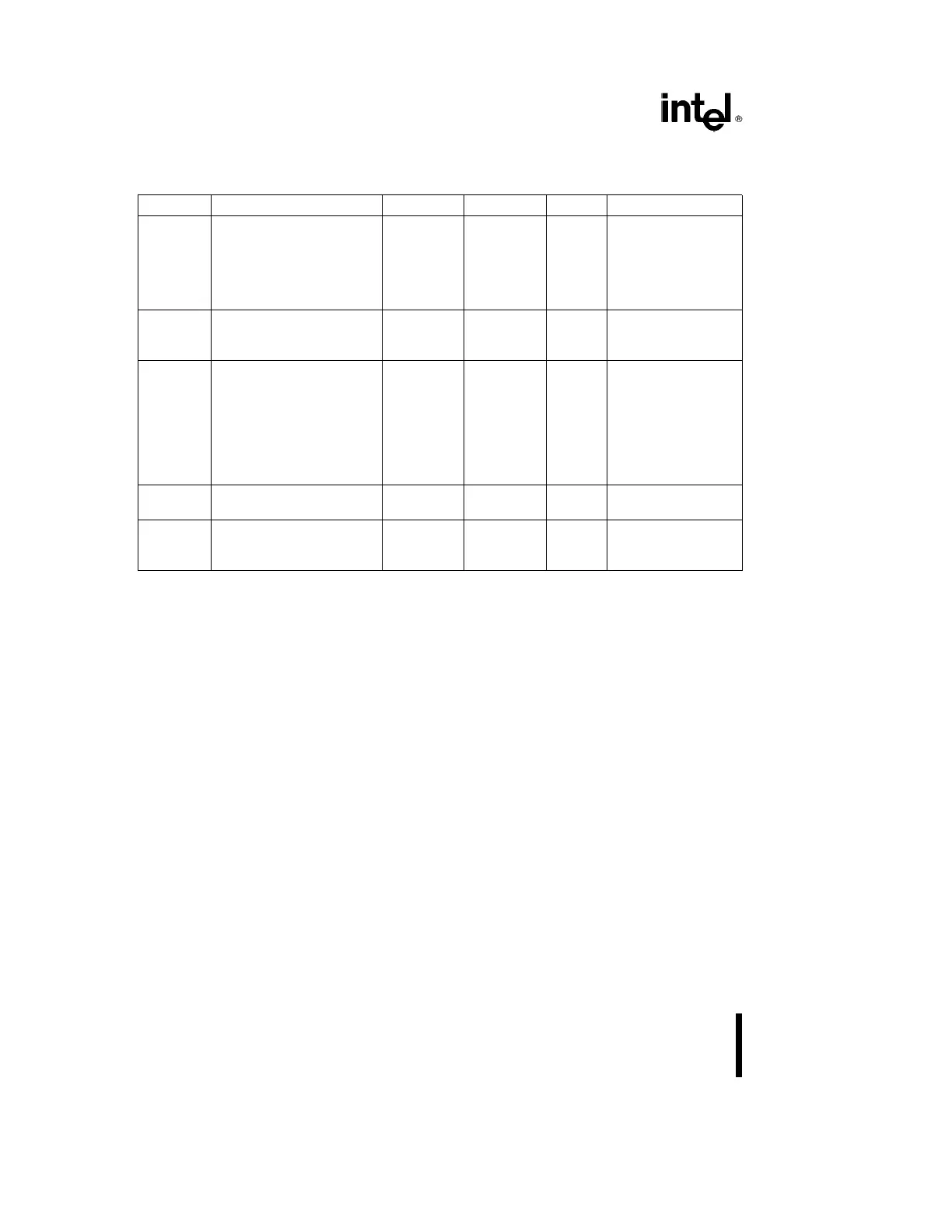

7.2 D.C. Characteristics

Table 7-1. D.C. Specifications T

C

e

0

§

Cto

a

100

§

C, V

CC

e

5V

g

10%

Symbol Parameter Min Max Units Test Conditions

V

IL

Input LO Voltage

b

0.3

a

0.8 V (Note 1)

V

IH

Input HI Voltage 2.0 V

CC

a

0.3 V (Note 1)

V

CL

CPUCLK2 and NUMCLK2

Input LO Voltage

b

0.3

a

0.8 V

V

CH

CPUCLK2 and NUMCLK2

Input HI Voltage V

CC

b

0.8 V

CC

a

0.8 V

V

OL

Output LO Voltage 0.45 V (Note 2)

V

OH

Output HI Voltage 2.4 V (Note 3)

V

OH

Output HI Voltage V

CC

b

0.8 V (Note 4)

I

CC

Power Supply Current

Dynamic Mode

Freq.

e

33 MHz

(5)

150 mA I

CC

typ.

e

135 mA

Freq.

e

25 MHz

(5)

150 mA I

CC

typ.

e

130 mA

Freq.

e

20 MHz

(5)

125 mA I

CC

typ.

e

110 mA

Freq.

e

16 MHz

(5)

100 mA I

CC

typ.

e

90 mA

Freq.

e

1 MHz

(5)

20 mA I

CC

typ.

e

5mA

Idle Mode

(6)

7mAI

CC

typ.

e

4mA

I

LI

Input Leakage Current

g

15 mA0V

s

V

IN

s

V

CC

I

LO

I/O Leakage Current

g

15 mA 0.45V

s

V

O

s

V

CC

C

IN

Input Capacitance 7 10 pF f

c

e

1 MHz

C

O

I/O Capacitance 7 12 pF f

c

e

1 MHz

C

CLK

Clock Capacitance 7 20 pF f

c

e

1 MHz

NOTES:

1. This parameter is for all inputs, excluding the clock inputs.

2. This parameter is measured at I

OL

as follows:

Data

e

4.0 mA

READYO

Ý

, ERROR

Ý

, BUSY

Ý

, PEREQ

e

25 mA

3. This parameter is measured at I

OH

as follows:

Data

e

1.0 mA

READYO

Ý

, ERROR

Ý

, BUSY

Ý

, PEREQ

e

0.6 mA

4. This parameter is measured at I

OH

as follows:

Data

e

0.2 mA

READYO

Ý

, ERROR

Ý

, BUSY

Ý

PEREQ

e

0.12 mA

5. Synchronous Clock Mode (CKM

e

1). I

CC

is measured at steady state, maximum capacitive loading on the outputs, and

worst-case D.C. level at the inputs.

6. Intel387 SX Math CoProcessor Internal Idle Mode. Synchronous clock mode, clock and control inputs are active but the

Math CoProcessor is not executing an instruction. Outputs driving CMOS inputs.

34

34

Loading...

Loading...