3/24/97 3-12 XA Memory Organization

3.6 Special Function Registers (SFRs)

Special Function Registers (SFRs) provide a means for programs to access CPU control and

status registers, peripheral devices, and I/O ports. The SFR mechanism provides a consistent

mechanism for accessing standard portions of the XA core, peripheral functions added to the

core within each XA derivative, and external devices as implemented in future derivatives.

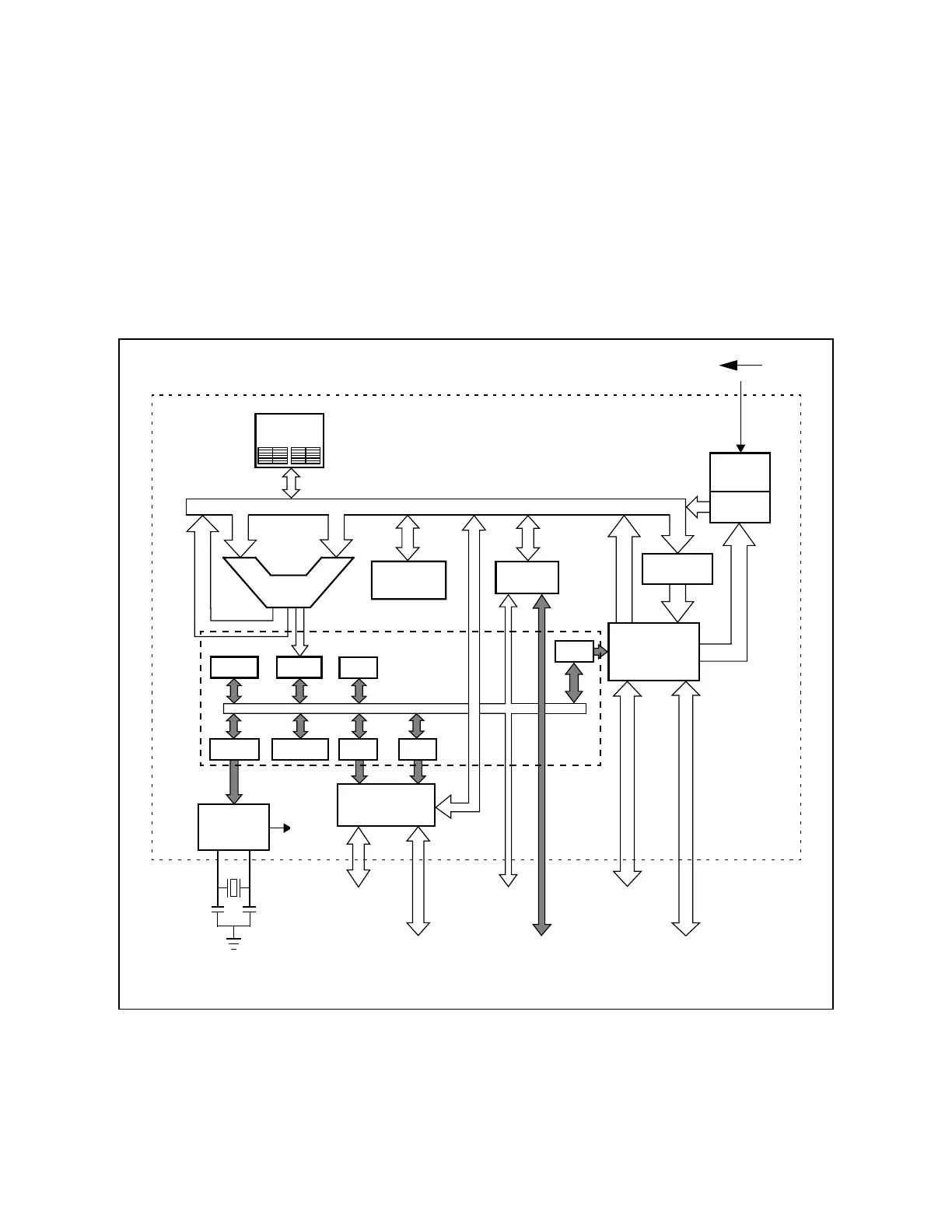

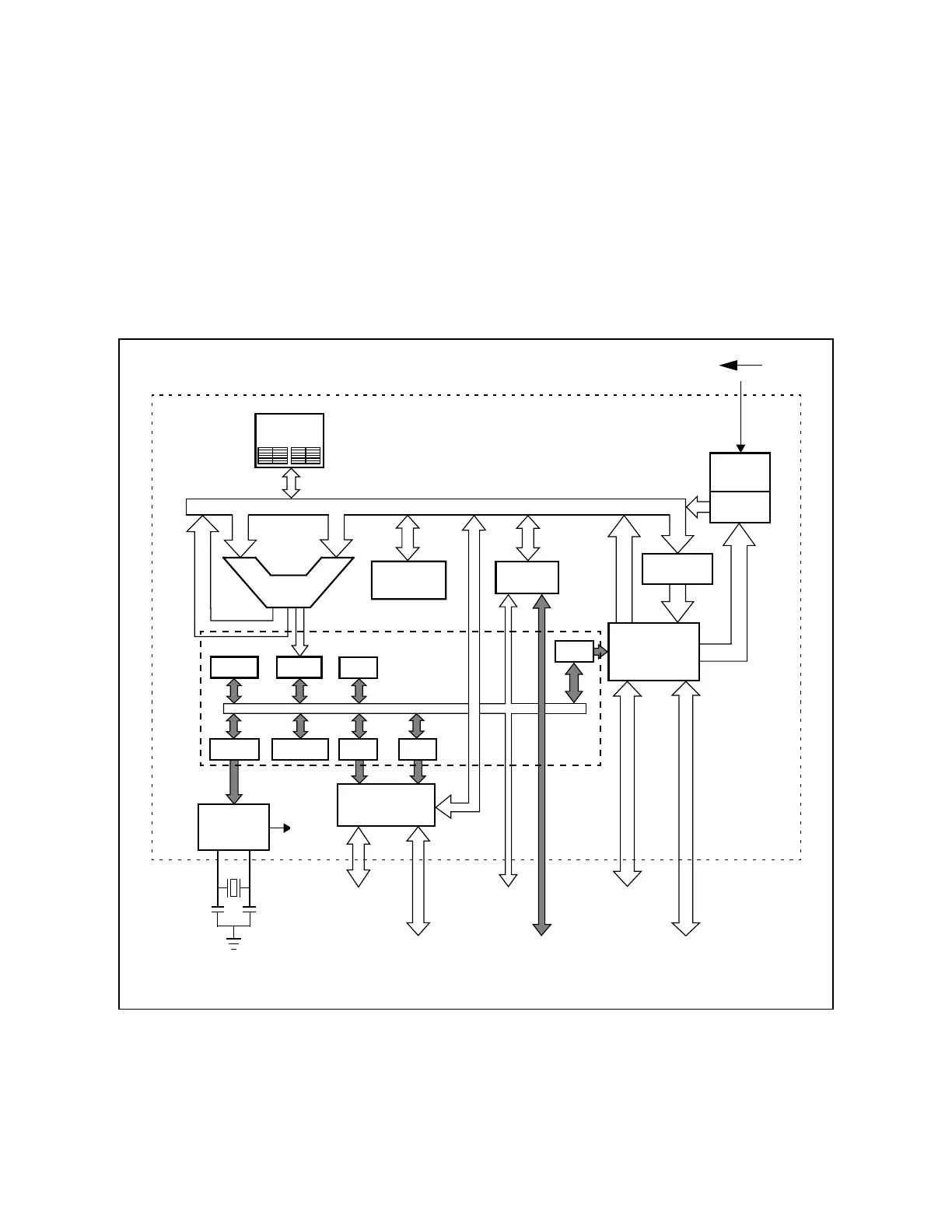

Figure 3.13 highlights the core registers that are accessed as SFRs: PCON, SCR, SSEL, PSWH,

PSWL, CS, ES, DS. Communication with these registers as well as on-chip peripheral devices

is performed via the dedicated Special Function Register Bus (see section 8).

The SFR address space is 1K bytes (Figure 3.14). The first half of this space (400h through

5FFh) is dedicated to accessing core registers and on-chip peripherals outside the XA core. SFRs

Figure 3.13 XA Core with SFRs highlighted

SFR bus

interface

Exception

Controller

Program

Counter

On-chip

Peripherals

On-chip

EPROM/

ROM

PSWL

PSWH

SCR

SSELPCON ES DS

Data/Address/Control Bus

RESET

Oscillator

16-bit

CS

External

Program

Memory

External

Data

Memory

On-chip

RAM

Program

Memory

Interface

ALU

16-bit

Data Memory

Interface

External

SFR

Devices

Register

File

Execution

Unit

IREG

CPU

Clock

SFR bus

8 or 16 bits

Loading...

Loading...