XA User Guide 3-11 3/24/97

3.5.2 External and Internal Overlap

If External Code Memory is placed by external logic at locations that overlap Internal Code

Memory, the Internal Code Memory takes precedence, and the overlapped portion of the

External memory will in not be accessed. However, on XA implementations that provide an

External Address (

EA) hardware input, setting EA low will cause external program memory to

be used.

3.5.3 Access

Code memory is intended to contain executable XA instructions. The XA architecture supports

storing constant data in Code Memory and provides special access modes for retrieving this

information. Constant data is implicitly stored within the instruction of many data manipulation

instructions when immediate operands are specified.

It is possible, and a common practice, to overlap external code and data memory spaces. In this

case it is important to understand that the memory spaces are logically separate. In such an

architecture, implemented with external logic, code memory is logically read-only memory that

is writable when accessed as external data memory. No such overlap is possible for internal code

memory.

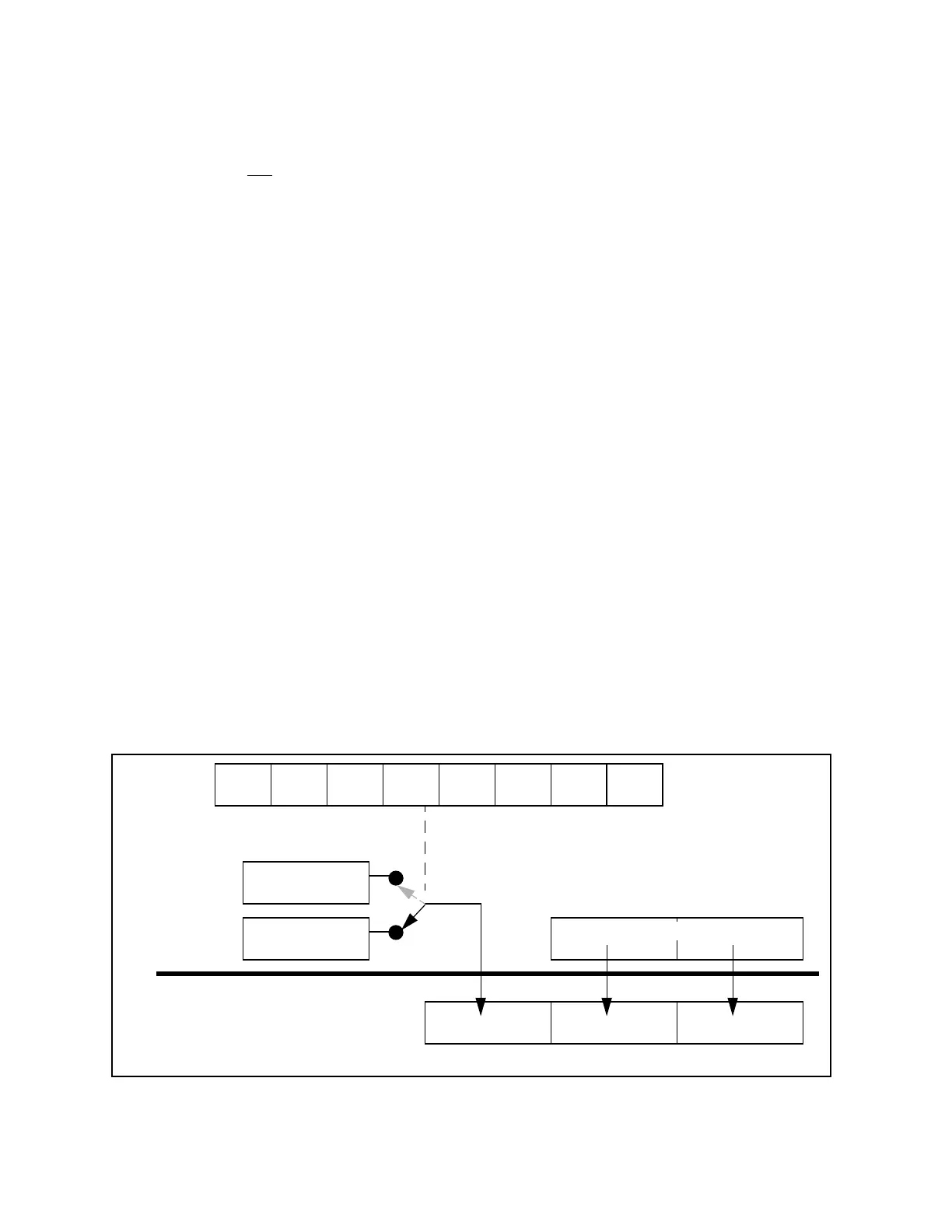

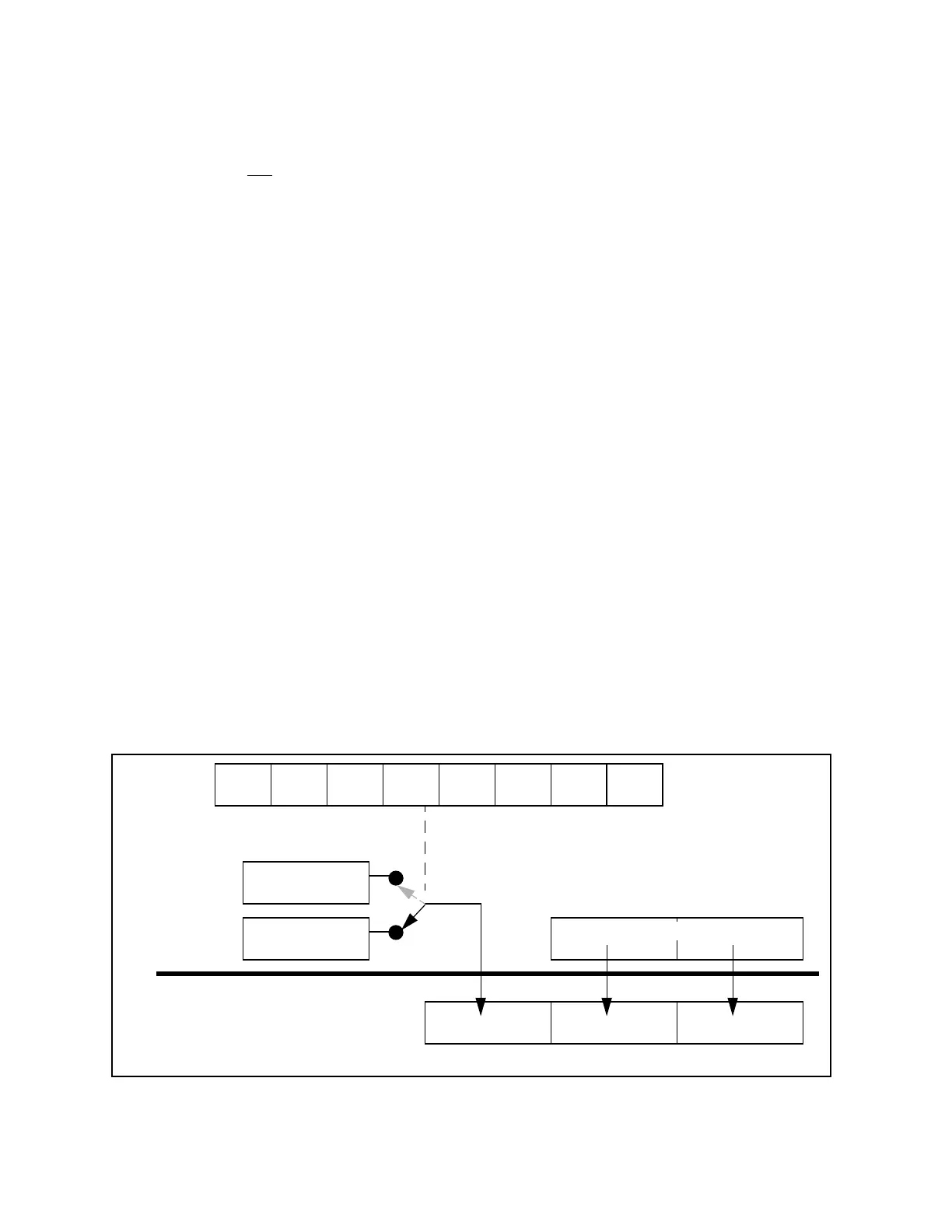

MOVC addressing in Code Memory

A special instruction, MOVC, is defined in the XA for accessing constant data (e.g lookup

tables, string constants etc.) stored in code memory. There is a standard form of MOVC that

reflects the native XA architecture, and there are two variations that reflect 80C51 compatibility;

see Chapter 9 for details of 80C51 compatibility. The standard form of MOVC uses a 16-bit

register value as a pointer, appended to either the top 8 bits of the Program Counter (PC) or the

Code Segment register (CS) to form a 24-bit address, as shown in Figure 3.12. The source for the

upper 8 address bits is determined by the setting of the segment selection bit (0 = PC and 1= CS)

in the SSEL register that corresponds to the operand register.

Figure 3.12 MOVC addressing in code memory

SSEL

ESWEN

R6SEG R5SEG R4SEG R3SEG R2SEG R1SEG

PC

CS R4

complete

24-bit memory

address

segment

registers

8-bit segment

identifier

16-bit segment offset

0

1

R0SEG

Loading...

Loading...