AP-578

2/21/97 12:57 PM 24329102.DOC

INTEL CONFIDENTIAL

(until publication date)

2. Alternatively, a software exception handler can

be invoked to handle the exception. When a

numeric exception is unmasked and the

exception occurs, the FPU stops further

execution of the numeric instruction and

causes a branch to a software exception

handler. The exception handler can then

implement any sort of recovery procedures

desired for any numeric exception detectable

by the FPU.

3.1.2 AUTOMATIC EXCEPTION HANDLING:

USING MASKED EXCEPTIONS

Each of the six exception conditions described

above has a corresponding flag bit in the FPU

status word and a mask bit in the FPU control word.

If an exception is masked (the corresponding mask

bit in the control word = 1), the processor takes an

appropriate default action and continues with the

computation. The processor has a default fix-up

activity for every possible exception condition it

may encounter. These masked-exception

responses are designed to be safe and are

generally acceptable for most numeric applications.

For example, if the Inexact result (Precision)

exception is masked, the system can specify

whether the FPU should handle a result that cannot

be represented exactly by one of four modes of

rounding: rounding it normally, chopping it toward

zero, always rounding it up, or always down. If the

Underflow exception is masked, the FPU will store

a number that is too small to be represented in

normalized form as a denormal (or zero if it’s

smaller than the smallest denormal). Note that

when exceptions are masked, the FPU may detect

multiple exceptions in a single instruction, because

it continues executing the instruction after

performing its masked response. For example, the

FPU could detect a denormalized operand, perform

its masked response to this exception, and then

detect an underflow.

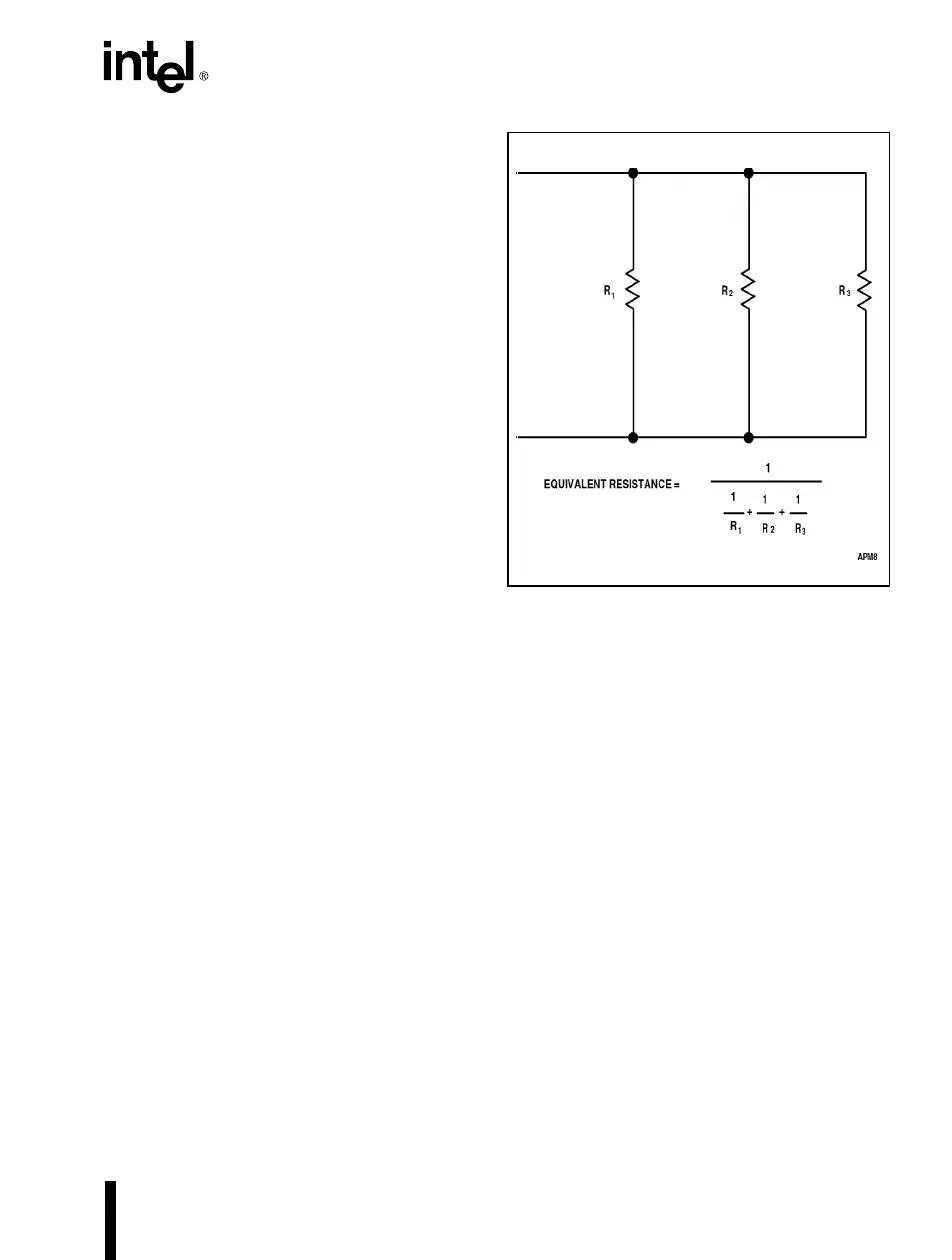

As an example of how even severe exceptions can

be handled safely and automatically using the

default exception responses, consider a calculation

of the parallel resistance of several values using

only the standard formula (Figure 4). If R1 becomes

zero, the circuit resistance becomes zero. With the

divide-by-zero and precision exceptions masked,

the processor will produce the correct result. FDIV

of R1 into 1 gives infinity, and then FDIV of (infinity

+R2 +R3) into 1 gives zero.

Figure 4. Arithmetic Example Using Infinity

By masking or unmasking specific numeric

exceptions in the FPU control word, programmers

can delegate responsibility for most exceptions to

the processor, reserving the most severe

exceptions for programmed exception handlers.

Exception-handling software is often difficult to

write, and the masked responses have been

tailored to deliver the most reasonable result for

each condition. For the majority of applications,

masking all exceptions yields satisfactory results

with the least programming effort. Certain

exceptions can usefully be left unmasked during the

debugging phase of software development, and

then masked when the clean software is actually

run. An invalid-operation exception for example,

typically indicates a program error that must be

corrected.

The exception flags in the FPU status word provide

a cumulative record of exceptions that have

occurred since these flags were last cleared. Once

set, these flags can be cleared only by executing

the FCLEX/FNCLEX (clear exceptions) instruction,

by reinitializing the FPU with FINIT/FNINIT or

FSAVE/FNSAVE, or by overwriting the flags with an

FRSTOR or FLDENV instruction. This allows a

programmer to mask all exceptions, run a

calculation, and then inspect the status word to see

Loading...

Loading...