XA User Guide 4-20 3/24/97

2. The breakpoint (caused by execution of the BKPT instruction, or a hardware breakpoint in an

emulation system) and Trace exceptions are intended to be mutually exclusive. In both cases, the

handler code will want to know the address in user code where the exception occurred. If a

breakpoint occurs during trace mode, or if trace mode is activated during execution of the

breakpoint handler code, one of the handlers will see a return address on the stack that points

within the other handler code.

Event Interrupts

Event Interrupts are typically related to on-chip or off-chip peripheral devices and so occur

asynchronously with respect to XA core activities. The XA core contains no inherent event

interrupt sources, so event interrupts are handled by an interrupt control unit that resides on-chip

but outside of the processor core.

On typical XA derivatives, event interrupts will arise from on-chip peripherals and from events

detected on interrupt input pins. Event interrupts may be globally disabled via the EA bit in the

Interrupt Enable register (IE) and individually masked by specific bits the IE register or its

extension. When an event interrupt for a peripheral device is disabled but the peripheral is not

turned off, the peripheral interrupt flag can still be set by the peripheral and an interrupt will

occur if the peripheral is re-enabled. An event interrupt that is enabled is serviced when its

priority is higher than that of the currently executing code. Each event interrupt is assigned a

priority level in the Interrupt Priority register(s). If more than one event interrupt occurs at the

same time, the priority setting will determine which one is serviced first. If more than one

interrupt is pending at the same level priority, a hardwares precedence scheme is used to choose

the first to service. The XA architecture defines 15 interrupt occurrence priorities that may be

programmed into the Interrupt Priority registers for Event Interrupts. Note that some XA

implementations may not support all 15 levels of occurrence priority. Consult the data sheet for a

specific XA derivative for details.

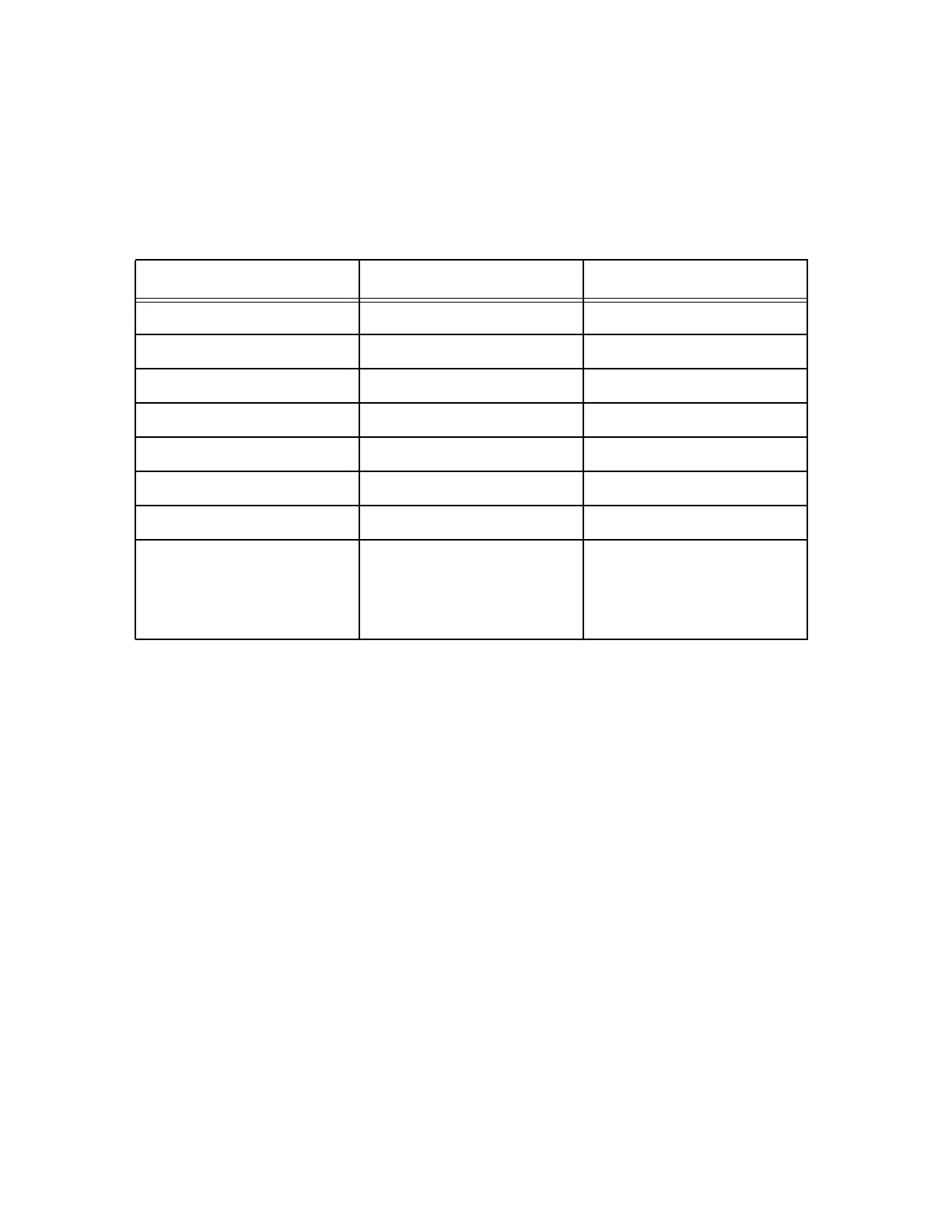

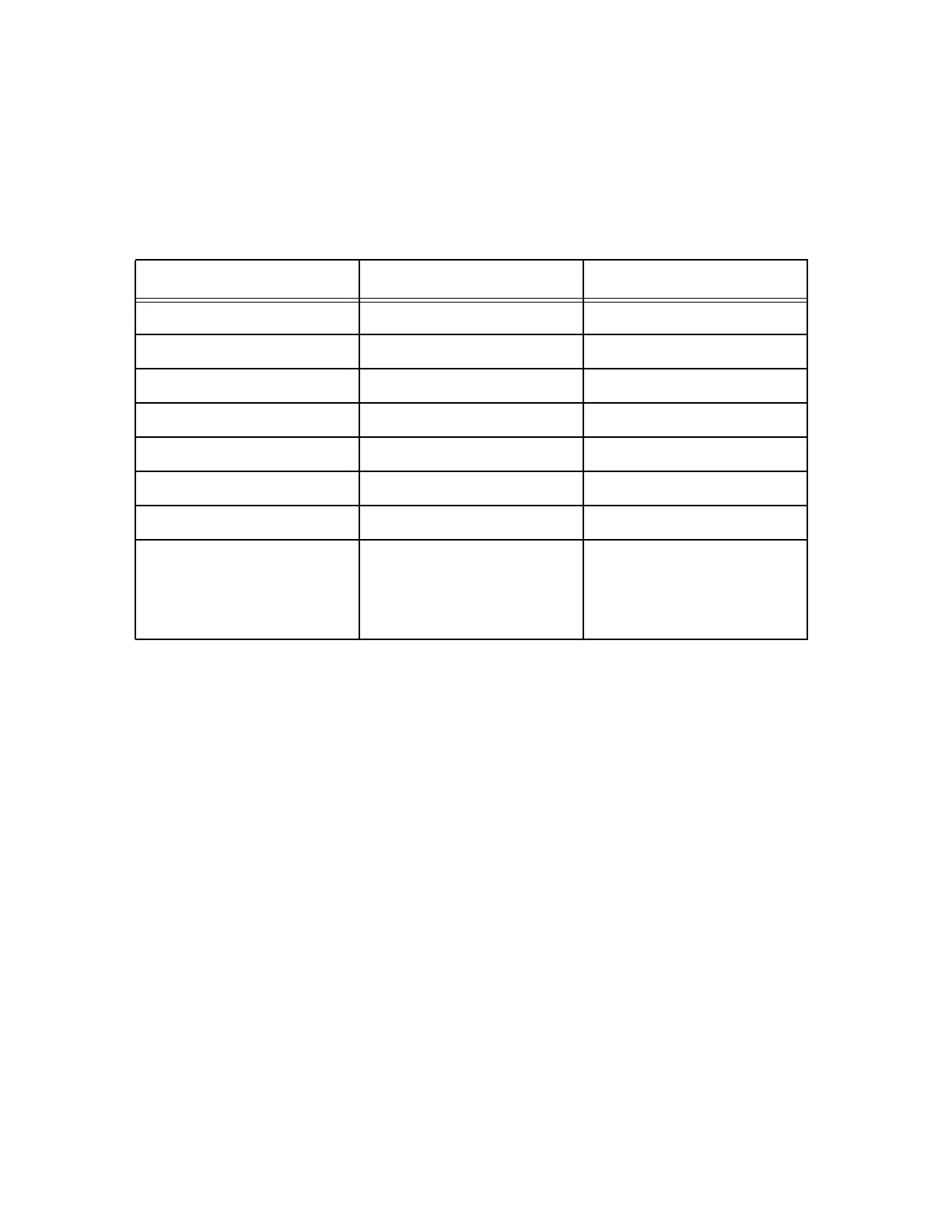

Table 4.1: Exception interrupts, vectors, and precedence

Exception Interrupt Vector Address Service Precedence

Breakpoint 0004h:0007h 0

Trace 0008h:000Bh 1

Stack Overflow 000Ch:000Fh 2

Divide-by-zero 0010h:0013h 3

User RETI 0014h:0017h 4

<reserved> 0018h - 003Fh 5

NMI 009Ch:009Fh 6

Reset 0000h:0003h 7

(always serviced

immediately, aborts

other exceptions)

Loading...

Loading...