XA User Guide 6-108 4/17/98

LSR Logical Shift Right

Syntax: LSR dest, count

Operation:

Description: If the count operand is greater than the variable specified by the destination

operand is logically shifted right by the number of bits specified by the count operand. The

MSBs of the result are filled with zeroes.The low-order bits are shifted out through the C (carry)

bit. If the count operand is 0, no shift is performed.The count operand is a positive value which

may be from 0 to 31. The data size may be 8, 16, or 32 bits. In the case of 32-bit shifts, the

destination operand must be the least significant half of a double word register. The count is not

affected by the operation.

Note:

- For Logical Shift Left, use ASL ignoring the N flag.

- If shift count (count in Rs) exceeds data size, the count value is truncated to 5 bits, else for

immediate shift count, shifting is continued until count is 0.

- a double word register is double-word aligned in the register file (R1:R0, R3:R2, R5:R4, or

R7:R6).

Size: Byte, Word, Double Word

Flags Updated: C, N, Z (N = 0 after an LSR unless count = 0, then it is unchanged)

LSR Rd, Rs (Rs = Byte-register)

Operation:

Bytes: 2

Clocks: For 8/16 bit shifts --> 4+1 for each 2 bits of shift

For 32 bit shifts --> 6+1 for each 2 bits of shift

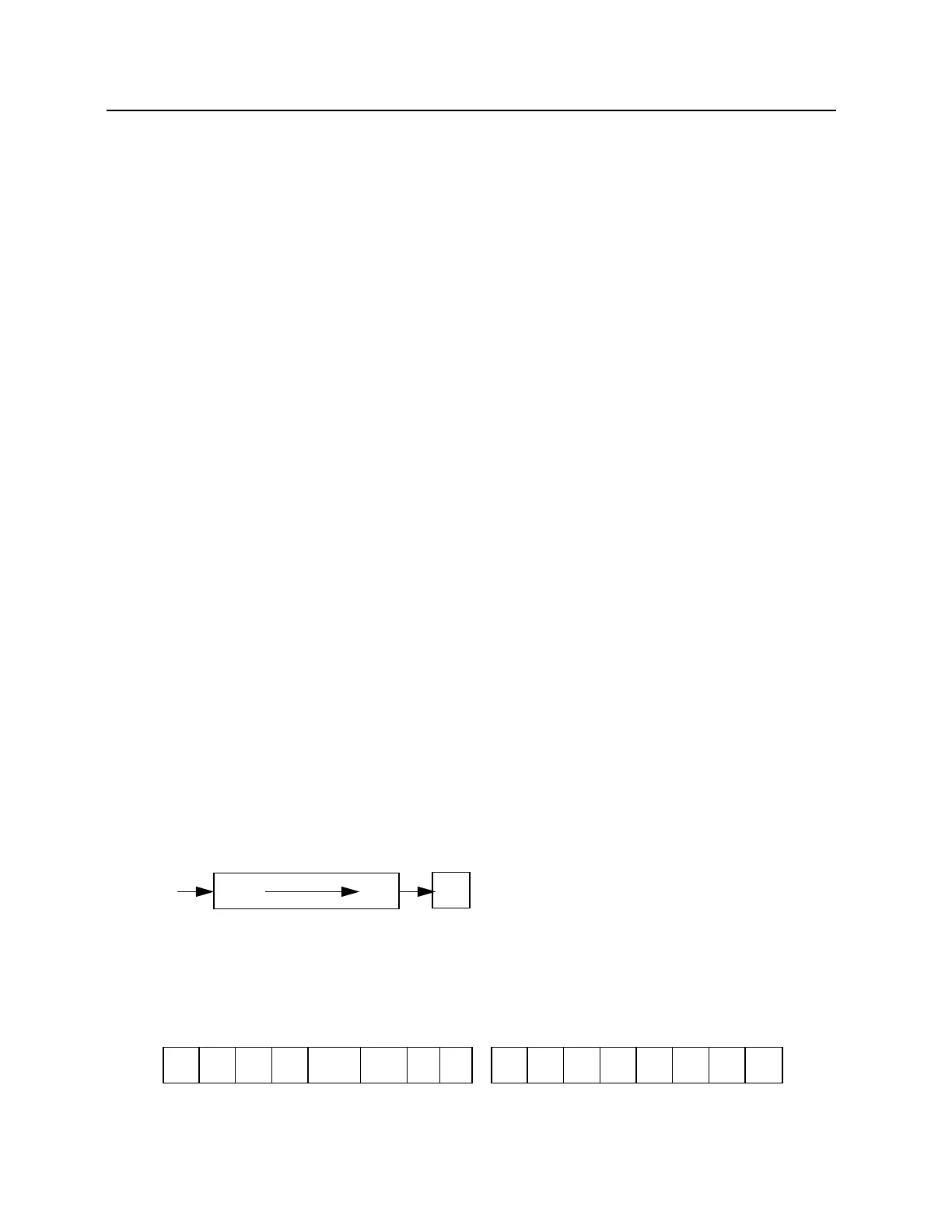

Encoding:

(C) <- (dest.0)

(dest.bit n) <- (dest.bit n+1)

count = count-1

Do While (count not equal to 0)

End While

(dest.msb) <- 0

CMSB0 LSB

(Rd)

d d d d s s s s

1 1 0 0 SZ1 SZ0 0 0

Loading...

Loading...