AP-578

2/21/97 12:57 PM 24329102.DOC

INTEL CONFIDENTIAL

(until publication date)

Intel486

,

Pentium

®

, or

Pentium Pro

processor

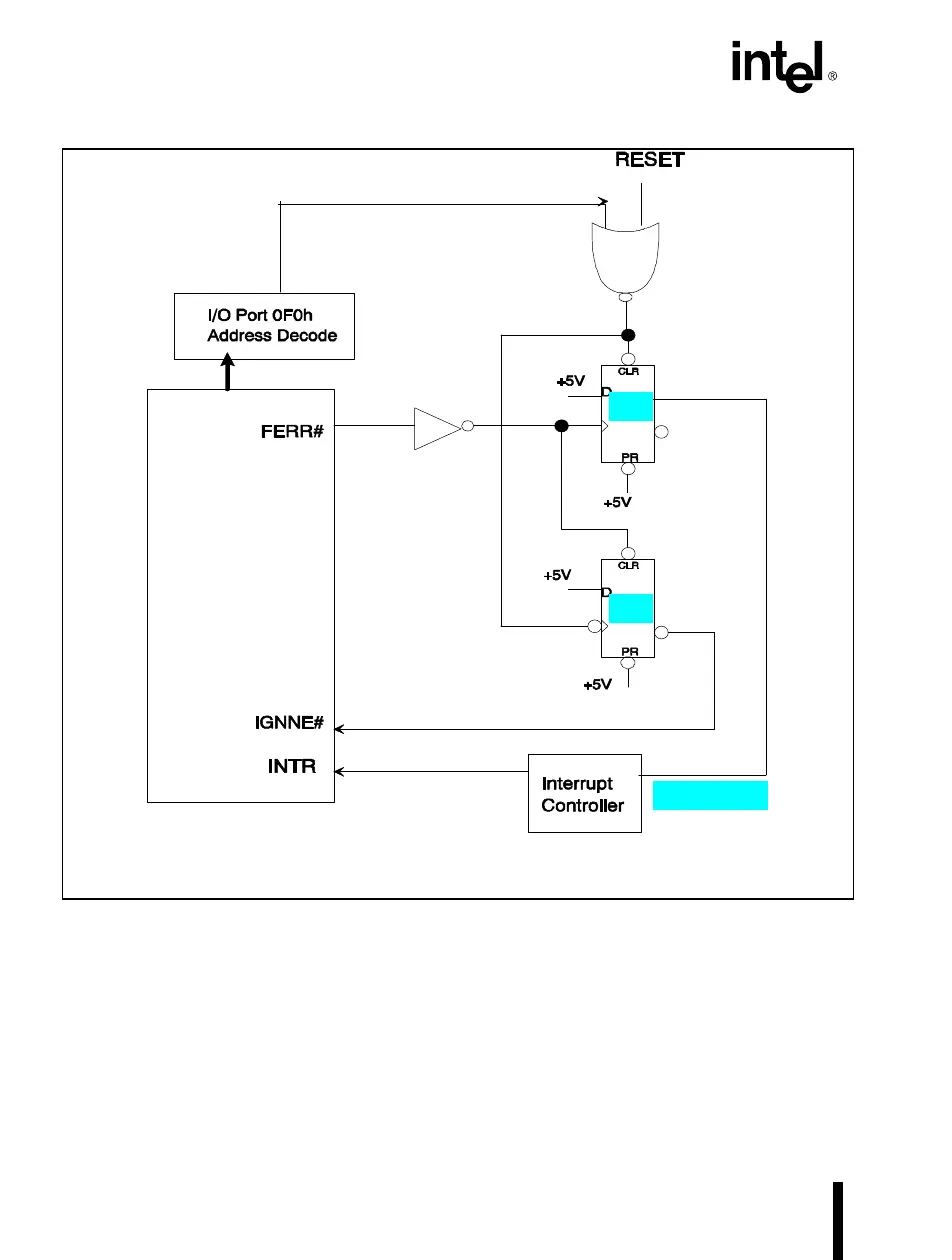

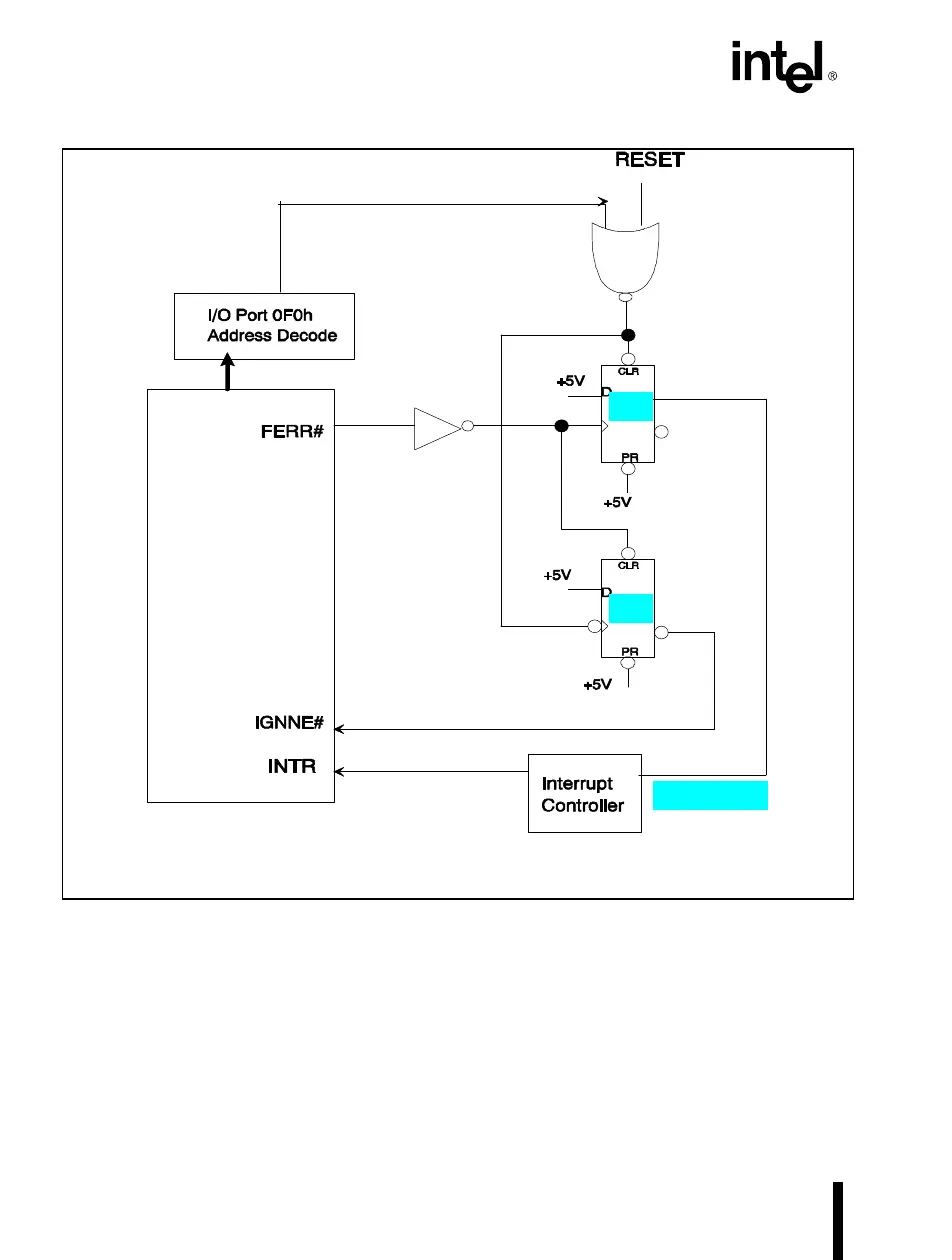

FF #1

FF #2

FP_IRQ

LEGEND

FF #n: Flip Flop #n

CLR: Clear or reset

Figure 1. Recommended Circuit for MS-DOS* Compatible FPU Exception Handling

the FPU exception condition (which de-asserts

FERR#). However, the circuit does not depend on

the order of actions by the FPU exception handler

to guarantee the correct hardware state upon exit

from the handler. The flip flop which drives IGNNE#

to the processor has its CLEAR input attached to

the inverted FERR#. This ensures that IGNNE# can

never be active when FERR# is inactive. So if the

handler clears the FPU exception condition before

the 0F0H access, IGNNE# does not get activated

and left on after exit from the handler.

2.3.3 “NO-WAIT” FPU INSTRUCTIONS CAN

GET FPU INTERRUPT IN WINDOW

The Pentium and the Intel486 processors

implement the “No-Wait” Floating-Point instructions

(FNINIT, FNCLEX, FNSTENV, FNSAVE, FNSTSW,

FNSTCW, FNENI, FNDISI or FNSETPM - See

Section 6.3.7 in the Pentium

®

Processor Family

Developer's Manual, Volume 3) in the MS-DOS

Compatibility mode (CR0.NE = 0) in the following

manner:

Loading...

Loading...