AP-578

2/21/97 12:57 PM 24329102.DOC

INTEL CONFIDENTIAL

(until publication date)

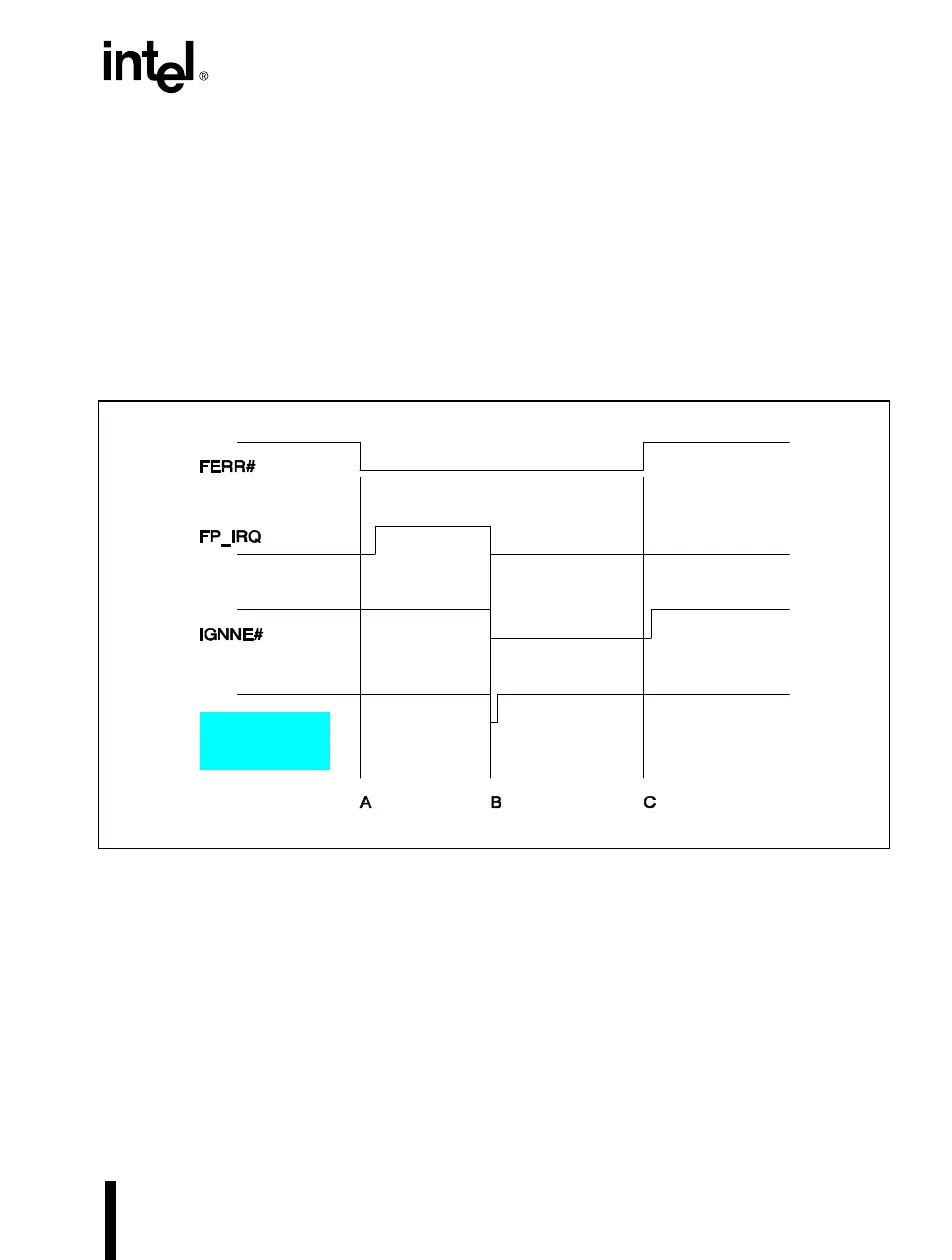

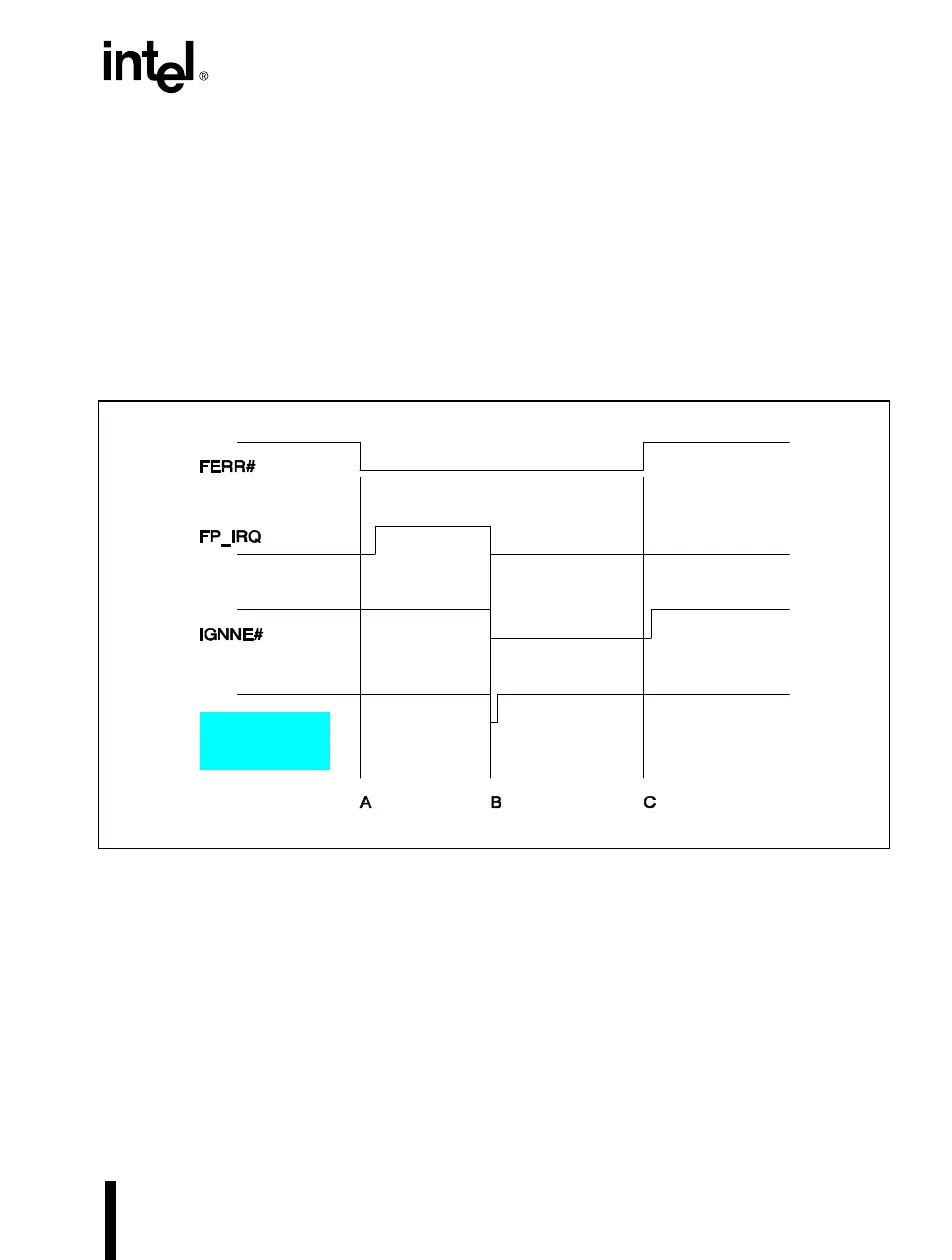

If an unmasked numeric exception is pending from

a preceding FPU instruction, a member of the “No-

Wait” class of instructions will, at the beginning of

its execution, assert the FERR# pin in response to

that exception just like other FPU instructions, but

then, unlike the other FPU instructions, FERR# will

be de-asserted. This de-assertion was implemented

to allow the “No-Wait” class of instructions to

proceed without an interrupt due to any pending

numeric exception. However, the brief assertion of

FERR# is sufficient to latch the FPU exception

request into most hardware interface

implementations (including Intel’s recommended

circuit).

All the FPU instructions are implemented such that

during their execution, there is a window in which

the processor will sample and accept external

interrupts. If there is a pending interrupt, the

processor services the interrupt first before

resuming the execution of the instruction.

Consequently, it is possible that the “No-Wait”

Floating-Point instruction may accept the external

interrupt caused by it’s own assertion of the FERR#

pin in the event of a pending unmasked numeric

exception, which is not an explicitly documented

behavior of a “No-Wait” instruction. This process is

illustrated by Figure 3, which is followed by a

detailed description of the several cases possible.

0F0H Address

Decode

Figure 2. Behavior of Signals During FPU Exception Handling

Loading...

Loading...