Intel387

TM

SX MATH COPROCESSOR

during the transitions to or from that state, the only

difference between a pipelined and a non-pipelined

cycle is the manner of changing from one state to

another. The exact activities during each state are

detailed in the previous section ‘‘Non-pipelined Bus

Cycles’’.

When the CPU asserts ADS

Ý

before the end of a

bus cycle, both ADS

Ý

and READY

Ý

are active dur-

ing a T

RS

state. This condition causes the Math Co-

Processor to change to a different state named T

P

.

One clock period after a T

P

state, the Math CoProc-

essor always returns to the T

RS

state. In consecu-

tive pipelined cycles, the Math CoProcessor bus log-

ic uses only the T

RS

and T

P

states.

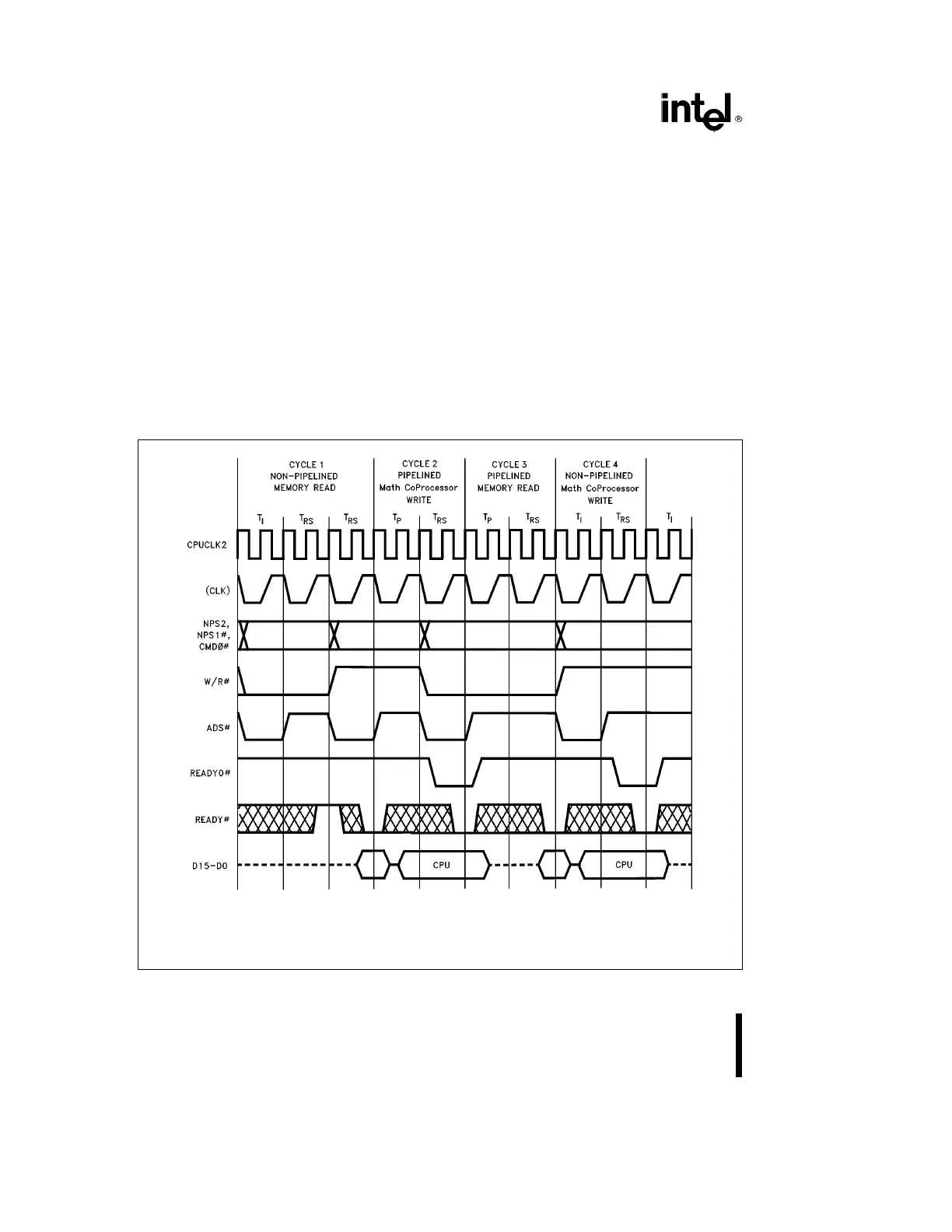

Figure 5-3 shows the fastest transitions into and out

of the pipelined bus cycles. Cycle 1 in the figure rep-

resents a non-pipelined cycle. (Non-pipelined write

are always followed by another non-pipelined cycle,

because READY

Ý

is asserted before the earliest

possible assertion of ADS

Ý

for the next cycle.)

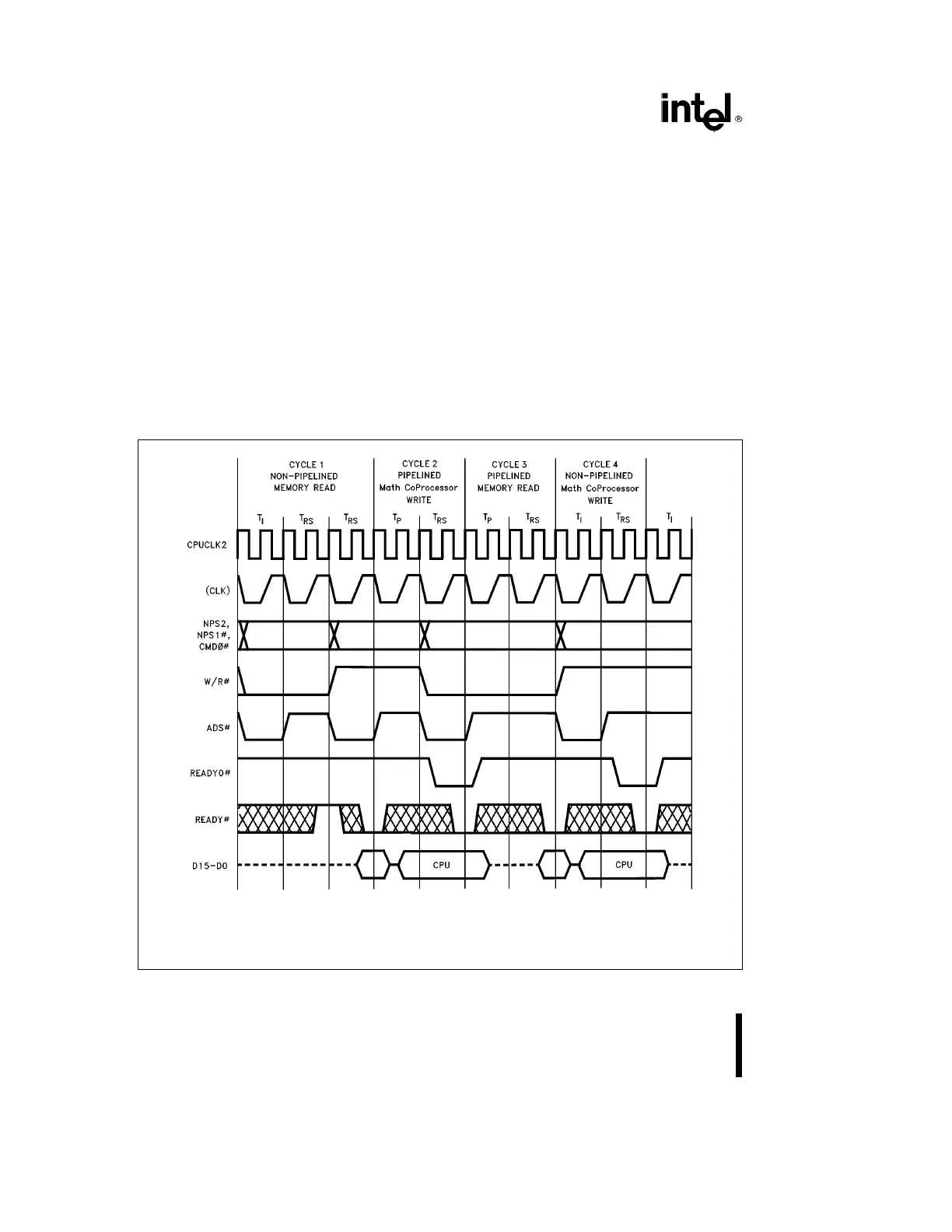

Figure 5-4 shows pipelined write and read cycles

with one additional T

RS

state beyond the minimum

required. To delay the assertion of READY

Ý

re-

quires external logic.

5.3 Mixed Bus Cycles

When the Math CoProcessor bus logic is in the T

RS

state, it distinguishes between non-pipelined and

pipelined cycles according to the behavior of ADS

Ý

and READY

Ý

. In a non-pipelined cycle, only

READY

Ý

is activated, and the transition is from the

T

RS

state to the idle state. In a pipelined cycle, both

READY

Ý

and ADS

Ý

are active, and the transition is

first from T

RS

state to T

P

state, then, after one clock

period, back to T

RS

state.

240225–9

Cycle 1 – Cycle 4 represent the operand transfer cycle for an instruction involving a transfer of two 32-bit loads in total.

The opcode write cycles and other overhead are not shown.

Note that the next cycle will be a pipelined cycle if both READY

Ý

and ADS

Ý

are sampled active at the end of a T

RS

state of the current cycle.

Figure 5-3. Fastest Transitions to and from Pipelined Cycles

30

30

Loading...

Loading...