80C187

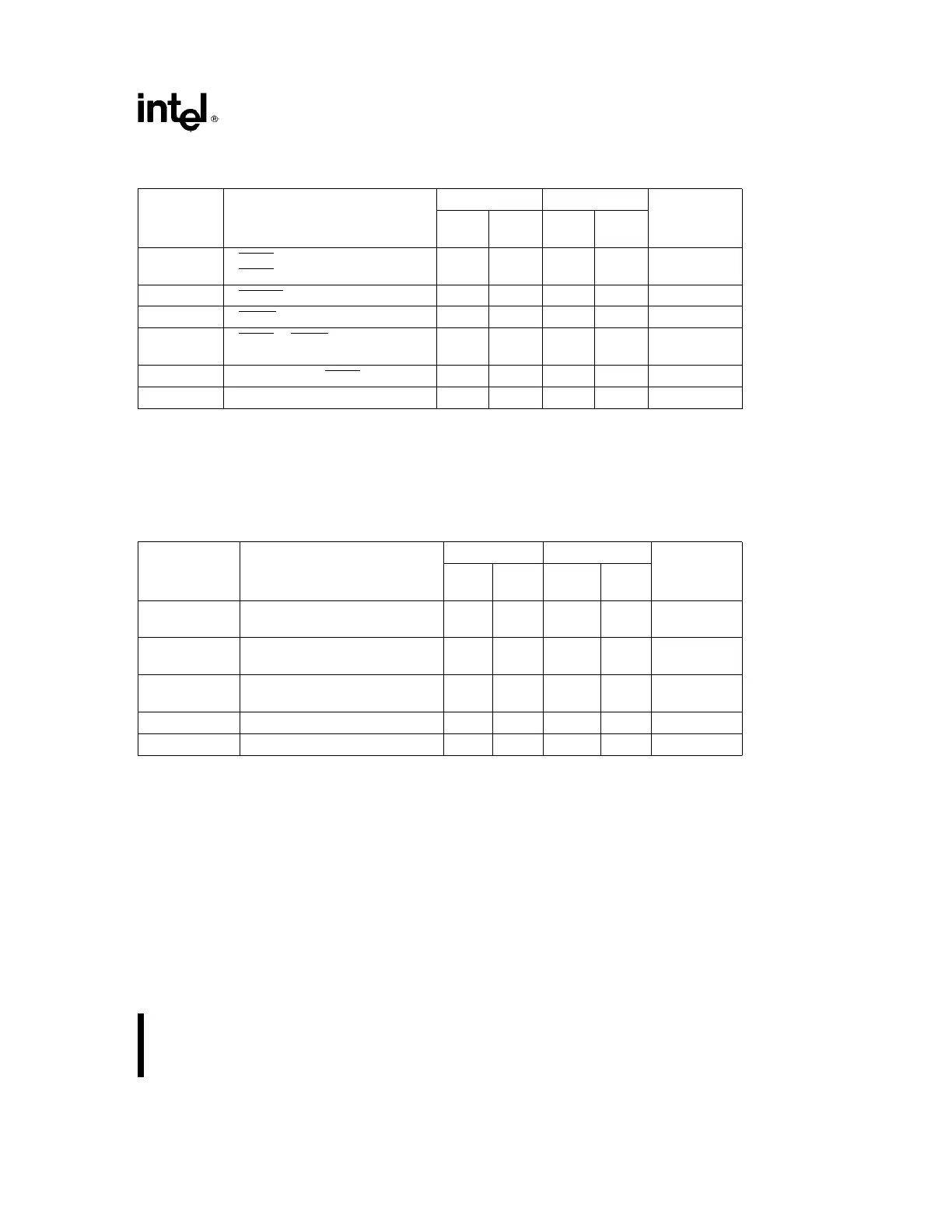

Timing Responses

All timings are measured at 1.5V unless otherwise specified

12.5 MHz 16 MHz

Test

Symbol Parameter Min Max Min Max Conditions

(ns) (ns) (ns) (ns)

T

rhqz

(t27) NPRD Inactive to Data Float* 18 18 Note 2

T

rlqv

(t28) NPRD Active to Data Valid 50 45 Note 3

T

ilbh

(t29) ERROR Active to Busy Inactive 104 104 Note 4

T

wlbv

(t30) NPWR Active to Busy Active 80 60 Note 4

T

klml

(t31) NPRD or NPWR Active 80 60 Note 5

to PEREQ Inactive

T

rhqh

(t32) Data Hold from NPRD Inactive 2 2 Note 3

T

rlbh

(t33) RESET Inactive to BUSY Inactive 80 60

NOTES:

*The data float delay is not tested.

2. The float condition occurs when the measured output current is less than I

OL

on D

15

–D

0

.

3. D

15

–D

0

loading: C

L

e

100 pF.

4. BUSY loading: C

L

e

100 pF.

5. On last data transfer of numeric instruction.

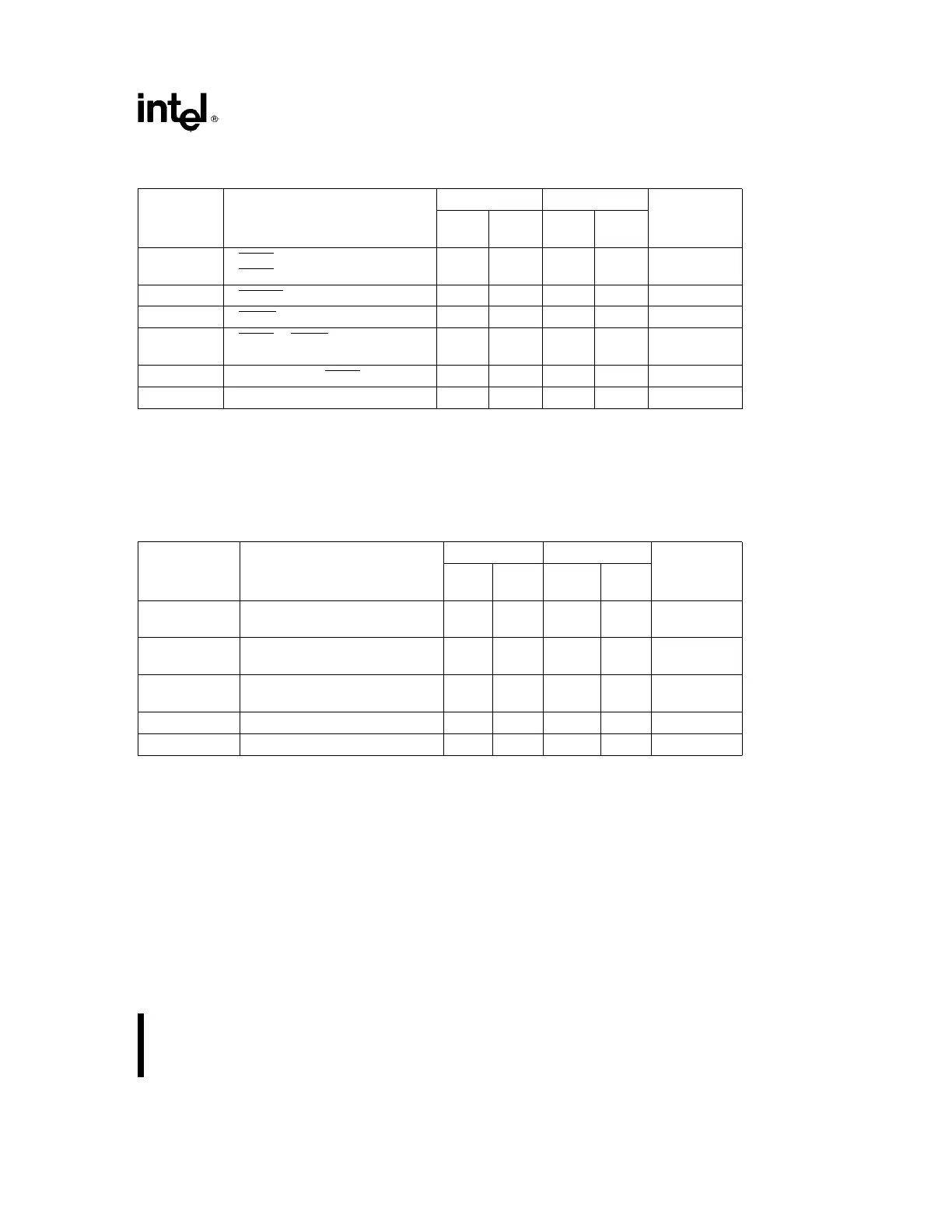

Clock Timings

12.5 MHz 16 MHz*

Test

Symbol Parameter Min Max Min Max Conditions

(ns) (ns) (ns) (ns)

T

clcl

(t1a) CLK Period CKM

e

1 80 250 N/A N/A Note 6

(t1B) CKM

e

0 40 125 31.25 125 Note 6

T

clch

(t2a) CLK Low Time CKM

e

1 35 N/A Note 6

(t2b) CKM

e

0 9 7 Note 7

T

chcl

(t3a) CLK High Time CKM

e

1 35 N/A Note 6

(t3b) CKM

e

0 13 9 Note 8

T

ch2ch1

(t4) 10 8 Note 9

T

ch1ch2

(t5) 10 8 Note 10

NOTES:

*16 MHz operation is available only in divide-by-2 mode (CKM strapped LOW).

6. At 1.5V

7. At 0.8V

8. At 2.0V

9. CKM

e

1: 3.7V to 0.8V at 16 MHz, 3.5V to 1.0V at 12.5 MHz

10. CKM

e

1: 0.8V to 3.7V at 16 MHz, 1.0V to 3.5V at 12.5 MHz

23

Loading...

Loading...