82C54

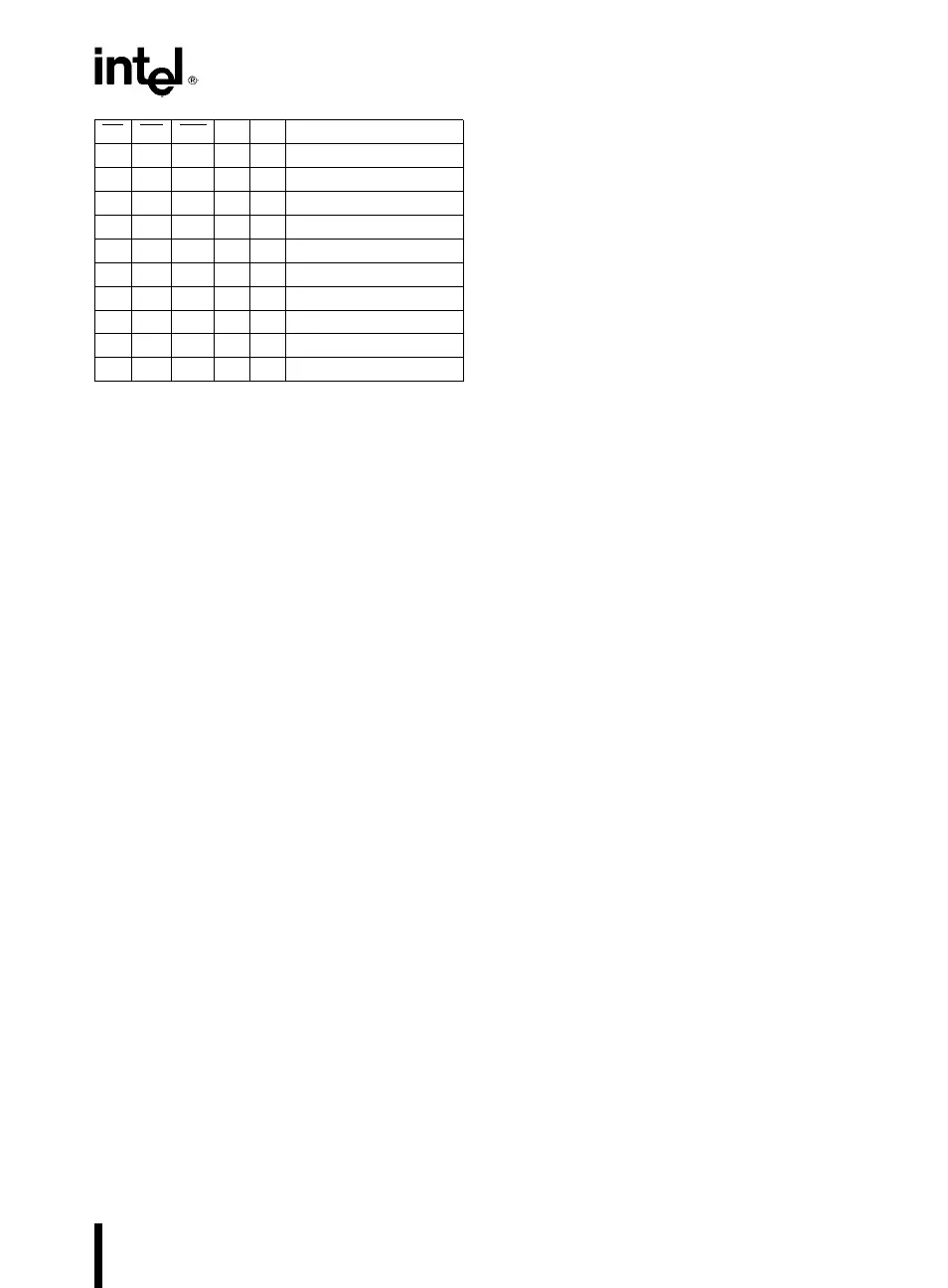

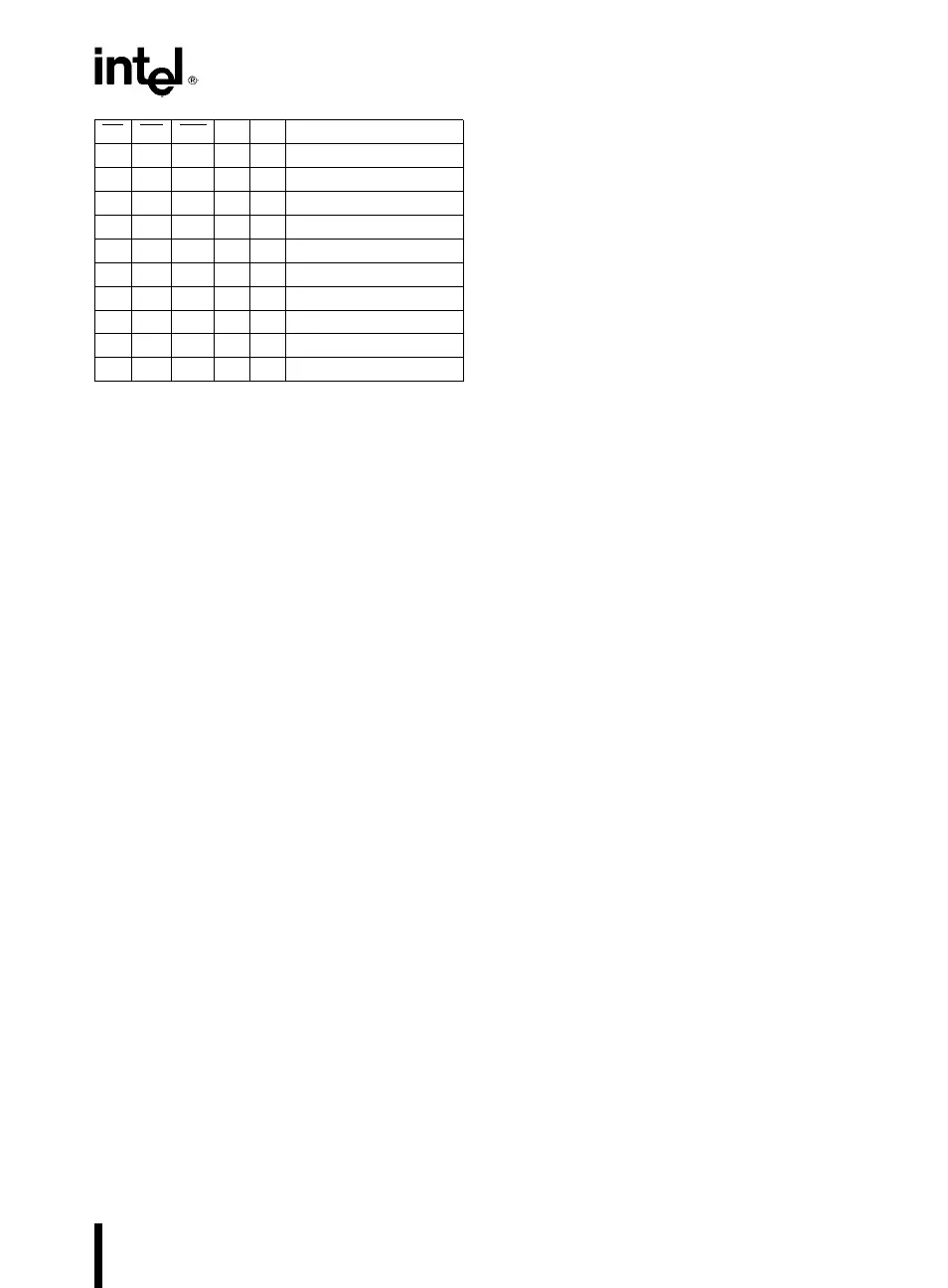

CS RD WR A

1

A

0

0 1 0 0 0 Write into Counter 0

0 1 0 0 1 Write into Counter 1

0 1 0 1 0 Write into Counter 2

0 1 0 1 1 Write Control Word

0 0 1 0 0 Read from Counter 0

0 0 1 0 1 Read from Counter 1

0 0 1 1 0 Read from Counter 2

0 0 1 1 1 No-Operation (3-State)

1 X X X X No-Operation (3-State)

0 1 1 X X No-Operation (3-State)

Figure 14. Read/Write Operations Summary

Mode Definitions

The following are defined for use in describing the

operation of the 82C54.

CLK PULSE: a rising edge, then a falling edge, in

that order, of a Counter’s CLK input.

TRIGGER: a rising edge of a Counter’s GATE in-

put.

COUNTER LOADING: the transfer of a count from

the CR to the CE (refer to

the ‘‘Functional Descrip-

tion’’)

MODE 0: INTERRUPT ON TERMINAL COUNT

Mode 0 is typically used for event counting. After the

Control Word is written, OUT is initially low, and will

remain low until the Counter reaches zero. OUT then

goes high and remains high until a new count or a

new Mode 0 Control Word is written into the Coun-

ter.

GATE

e

1 enables counting; GATE

e

0 disables

counting. GATE has no effect on OUT.

After the Control Word and initial count are written to

a Counter, the initial count will be loaded on the next

CLK pulse. This CLK pulse does not decrement the

count, so for an initial count of N, OUT does not go

high until N

a

1 CLK pulses after the initial count is

written.

If a new count is written to the Counter, it will be

loaded on the next CLK pulse and counting will con-

tinue from the new count. If a two-byte count is writ-

ten, the following happens:

1) Writing the first byte does not disable counting.

OUT is set low immediately (no clock pulse re-

quired).

2) Writing the second byte allows the new count to

be loaded on the next CLK pulse.

3) When there is a count in progress, writing a new

LSB before the counter has counted down to 0

and rolled over to FFFFh, WILL stop the counter.

However, if the LSB is loaded AFTER the counter

has rolled over to FFFFh, so that an MSB now

exists in the counter, then the counter WILL NOT

stop.

This allows the counting sequence to be synchroniz-

ed by software. Again, OUT does not go high until N

a

1 CLK pulses after the new count of N is written.

9

Loading...

Loading...