XA User Guide 2-5 3/24/97

chip space always begins at code address 0 and extends to the limit of the on-chip code memory.

Above that, code will be fetched from off-chip. Most XA derivatives will support an external bus

for off-chip data and code memory, and may also be used in a ROM-less mode, with no code

memory used on-chip.

In some cases, code memory may be addressed as data. Special instructions provide access to the

entire code space via pointers. Either a special segment register (CS or Code Segment) or the

upper 8-bits of the Program Counter (PC) may be used to identify the portion of code memory

referenced by the pointer.

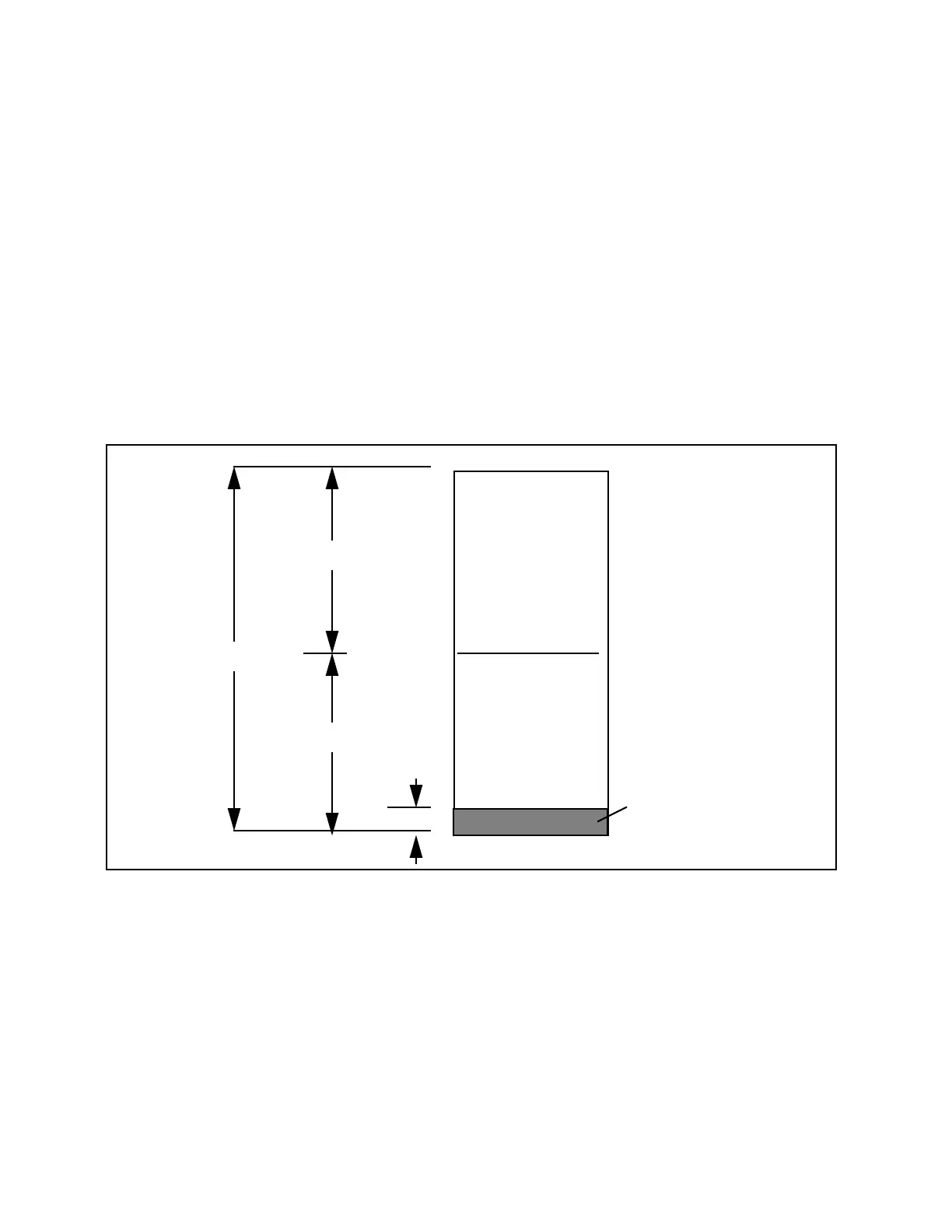

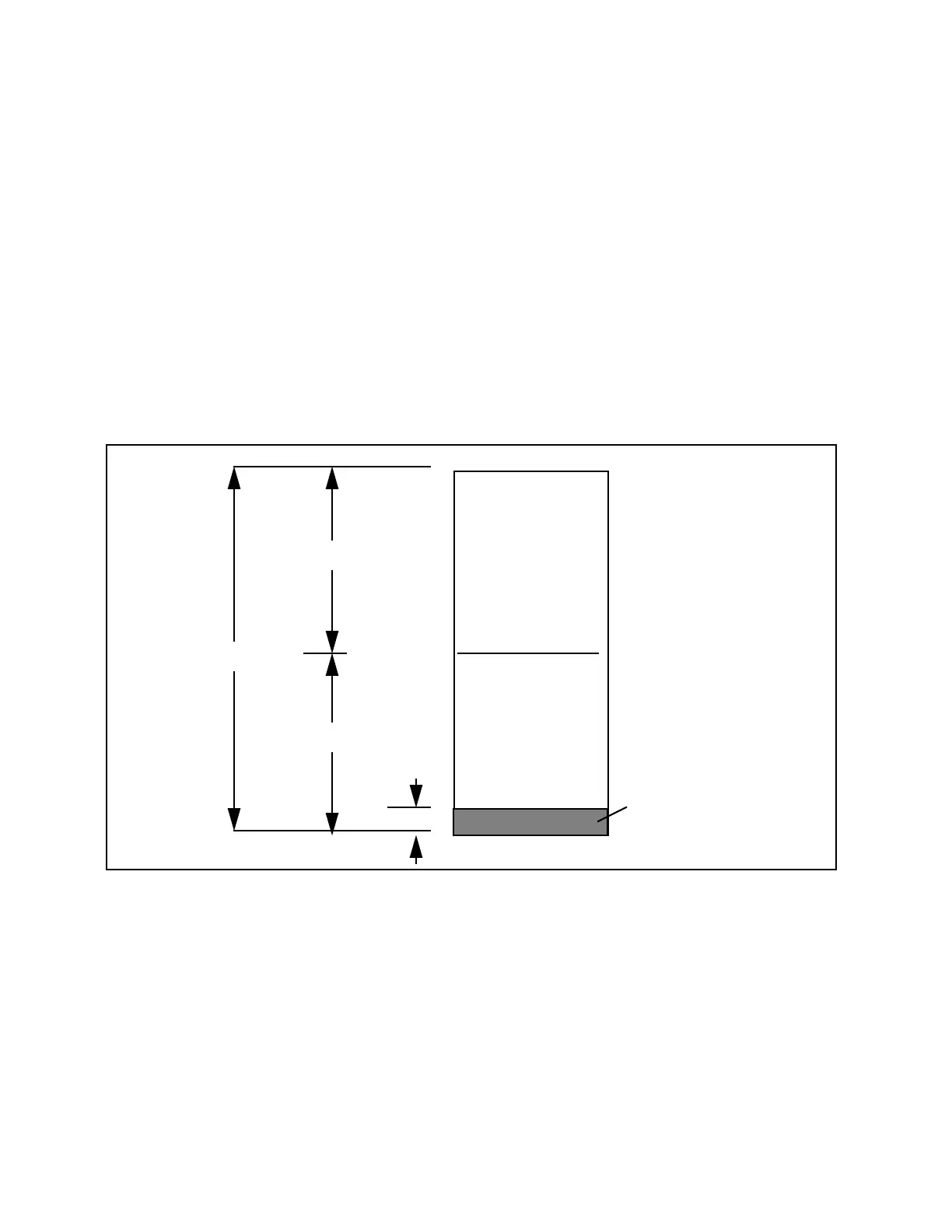

2.2.4 Special Function Registers

Special Function Registers (SFRs) provide a means for the XA to access Core registers, internal

control registers, peripheral devices, and I/O ports. Any SFR may be accessed by a program at

any time without regard to any pointer or segment. An SFR address is always contained entirely

within an instruction. See Figure 2.5.

The total SFR space is 1K bytes in size. This is further divided into two 512 byte regions. The

lower half is assigned to on-chip SFRs, while the second half is reserved for off-chip SFRs. This

allows provides a means to add off-chip I/O devices mapped into the XA as SFRs. Off-chip SFR

access is not implemented on all XA derivatives.

On-chip SFRs are implemented as needed to provide control for peripherals or access to CPU

features and functions. Each XA derivative may have a different number of SFRs implemented

Figure 2.5 SFR Address Space

Bit-Addressable

1 K bytes

Off-Chip

SFRs

On-Chip

SFRs

512 bytes

512 bytes

64 bytes

Loading...

Loading...