3/24/97 2-4 Architectural Overview

Direct. The first 1K bytes of data on each segment may be accessed by an address contained

within the instruction.

Indirect. A complete 24-bit data memory address is formed by an 8-bit segment register

concatenated with 16-bits from a pointer register.

Indirect with offset. An 8-bit or 16-bit signed offset contained within the instruction is added to

the contents of a pointer register, then concatenated with an 8-bit segment register to produce a

complete address. This mode allows access into a data structure when a pointer register contains

the starting address of the structure. It also allows subroutines to access parameters passed on the

stack.

Indirect with auto-increment. The address is formed in the same manner as plain indirect, but the

pointer register contents are automatically incremented following the operation.

Data movement instructions and some special purpose instructions also have additional data

addressing modes.

The XA data memory addressing scheme provides for upward compatibility with the 80C51. For

details, refer to Chapter 9.

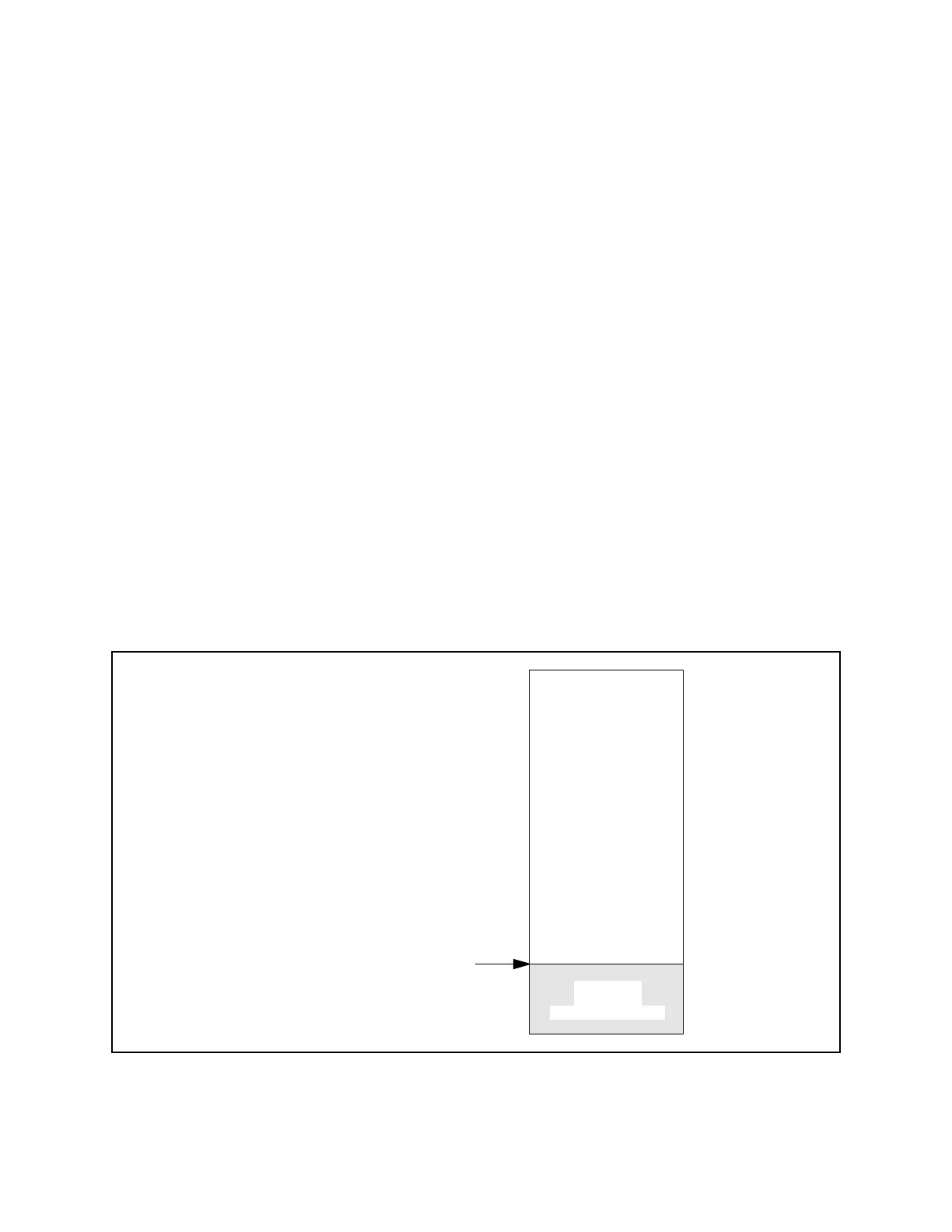

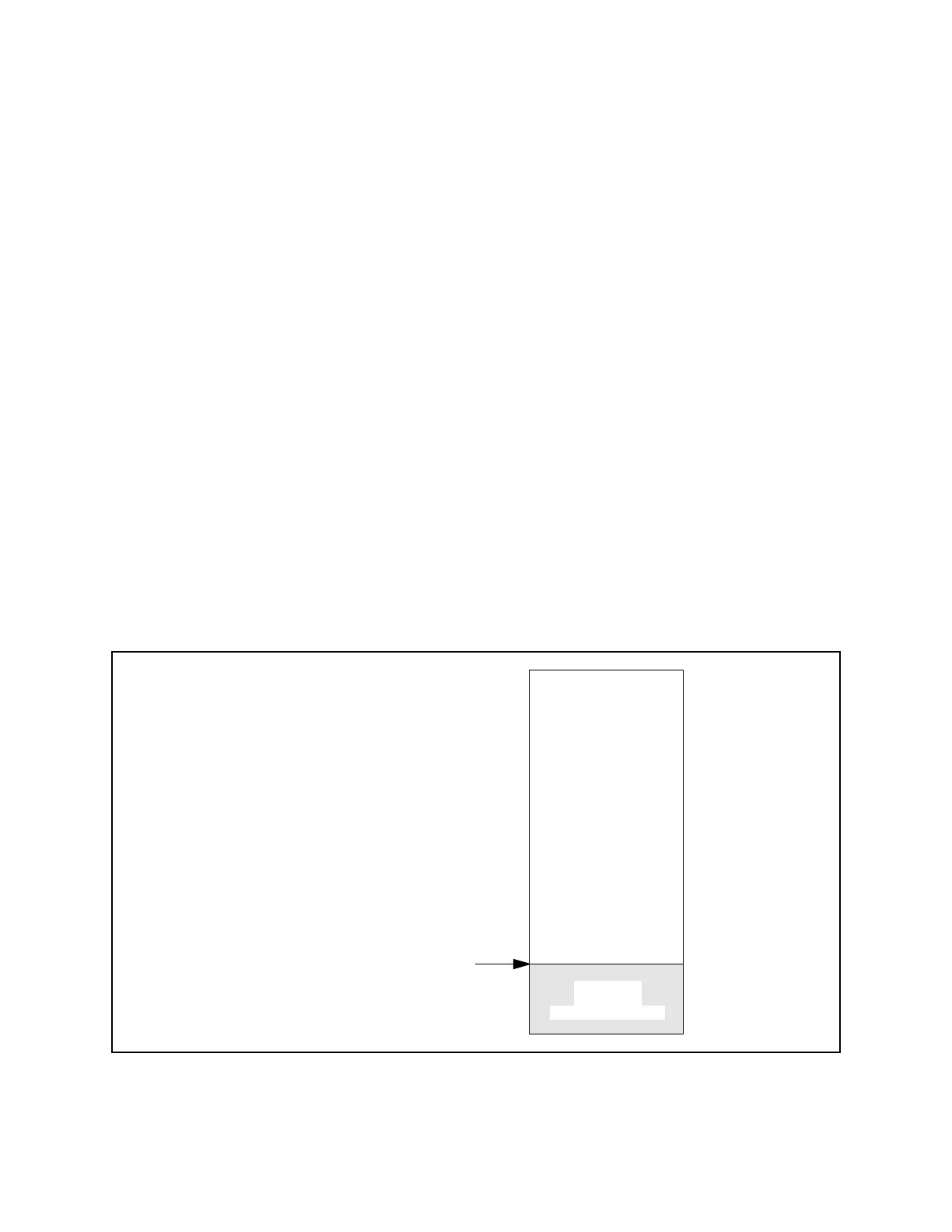

2.2.3 Code Memory

The XA is a Harvard architecture device, meaning that the code and data spaces are separate.

The XA provides a continuous, unsegmented linear code space that may be as large as 16

megabytes (Figure 2.4). In XA derivatives with on-chip ROM or EPROM code memory, the on-

Figure 2.4 XA code memory map

0

FFFFFFh (16M)

16 Mbytes of linear

code space

The on-chip/off-chip code

memory boundary varies

for different XA derivatives

On-chip

code memory

Off-chip

code memory

Loading...

Loading...