4-2

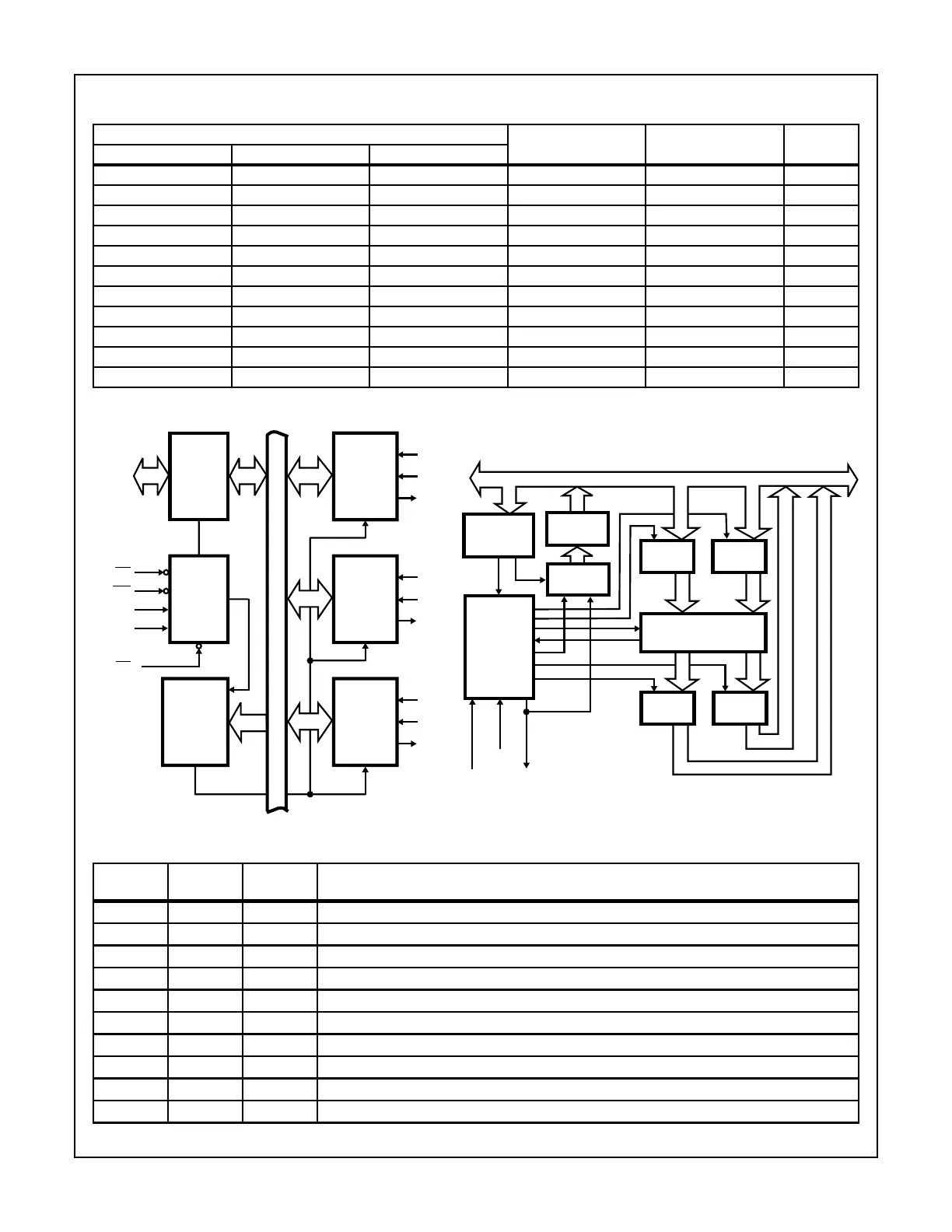

Functional Diagram

Ordering Information

PART NUMBERS

TEMPERATURE

RANGE PACKAGE PKG. NO.8MHz 10MHz 12MHz

CP82C54 CP82C54-10 CP82C54-12 0

o

C to +70

o

C 24 Lead PDIP E24.6

IP82C54 IP82C54-10 IP82C54-12 -40

o

C to +85

o

C 24 Lead PDIP E24.6

CS82C54 CS82C54-10 CS82C54-12 0

o

C to +70

o

C 28 Lead PLCC N28.45

IS82C54 IS82C54-10 IS82C54-12 -40

o

C to +85

o

C 28 Lead PLCC N28.45

CD82C54 CD82C54-10 CD82C54-12 0

o

C to +70

o

C 24 Lead CERDIP F24.6

ID82C54 ID82C54-10 ID82C54-12 -40

o

C to +85

o

C 24 Lead CERDIP F24.6

MD82C54/B MD82C54-10/B MD82C54-12/B -55

o

C to +125

o

C 24 Lead CERDIP F24.6

MR82C54/B MR82C54-10/B MR82C54-12/B -55

o

C to +125

o

C 28 Lead CLCC J28.A

SMD # 8406501JA - 8406502JA -55

o

C to +125

o

C 24 Lead CERDIP F24.6

SMD# 84065013A - 84065023A -55

o

C to +125

o

C 28 Lead CLCC J28.A

CM82C54 CM82C54-10 CM82C54-12 0

o

C to +70

o

C 24 Lead SOIC M24.3

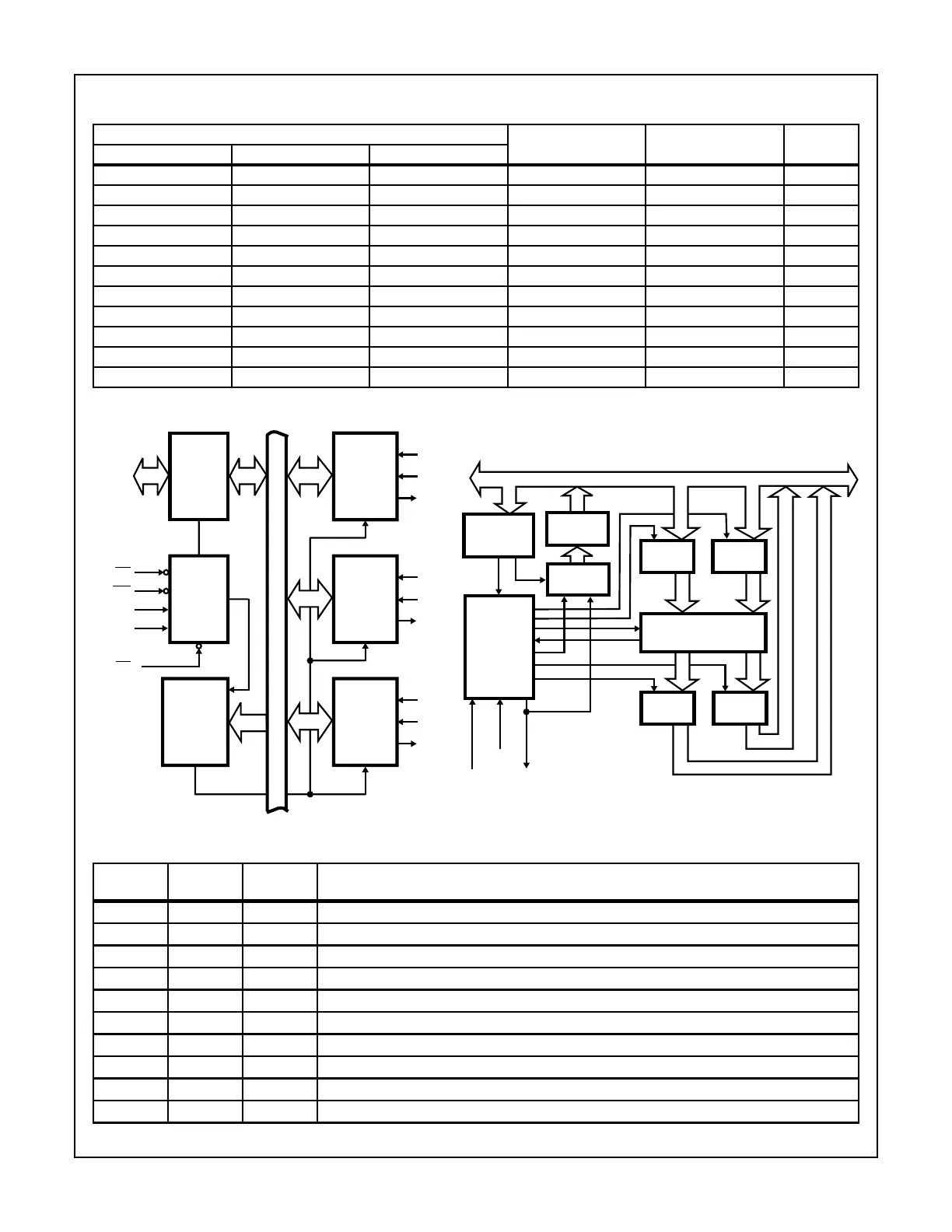

Pin Description

SYMBOL

DIP PIN

NUMBER TYPE DEFINITION

D7 - D0 1 - 8 I/O DATA: Bi-directional three-state data bus lines, connected to system data bus.

CLK 0 9 I CLOCK 0: Clock input of Counter 0.

OUT 0 10 O OUT 0: Output of Counter 0.

GATE 0 11 I GATE 0: Gate input of Counter 0.

GND 12 GROUND: Power supply connection.

OUT 1 13 O OUT 1: Output of Counter 1.

GATE 1 14 I GATE 1: Gate input of Counter 1.

CLK 1 15 I CLOCK 1: Clock input of Counter 1.

GATE 2 16 I GATE 2: Gate input of Counter 2.

OUT 2 17 O OUT 2: Output of Counter 2.

CONTROL

WORD

REGISTER

READ/

WRITE

LOGIC

DATA/

BUS

BUFFER

COUNTER

2

COUNTER

1

COUNTER

0

INTERNAL BUS

INTERNAL BUS

CONTROL

LOGIC

CONTROL

WORD

REGISTER

STATUS

LATCH

STATUS

REGISTER

CLK n

GATE n

OUT n

OUT 2

GATE 2

CLK 2

OUT 1

GATE 1

CLK 1

OUT 0

GATE 0

CLK 0

WR

RD

D

7

- D

0

A

0

A

1

CS

OL

M

OL

L

CE

CR

M

CR

L

COUNTER INTERNAL BLOCK DIAGRAM

8

82C54

Loading...

Loading...