4/17/98 6-1 Addressing Modes and Data Types

6 Instruction Set and Addressing

This section contains information about the addressing modes and data types used in the XA.

The intent is to help the user become familiar with the programming capabilities of the

processor.

6.1 Addressing Modes

Addressing modes are ways to form effective addresses of the operands. The XA provides seven

basic powerful addressing modes for access on word, byte, and bit data, or to specify the target

address of a branch instruction. These basic addressing modes are uniformly available on a large

number of instructions. Table 6.1 includes the basic addressing modes in the XA. An instruction

could use a combination of these basic addressing modes, e.g., ADD R0, #020 is a combination

of Register and Immediate addressing modes.

All modes (non-register) generate ADDR[15:0]. This address is combined with DS/ES[23:16]

for data and PC/CS[23:16] for code to form a 24-bit address

1

.

An XA instruction can have zero, one, two, or three operands, whose locations are defined by the

addressing mode. A destination operand is one that is replaced by a result, or is in some way

affected by the instruction. The destination operand is listed first in an addressing mode

expression. A source operand is a value that is moved or manipulated by the instruction, but is

not altered. The source is listed second in an addressing mode expression.

1. Exception is Page 0 mode, where all addresses are 16-bit.

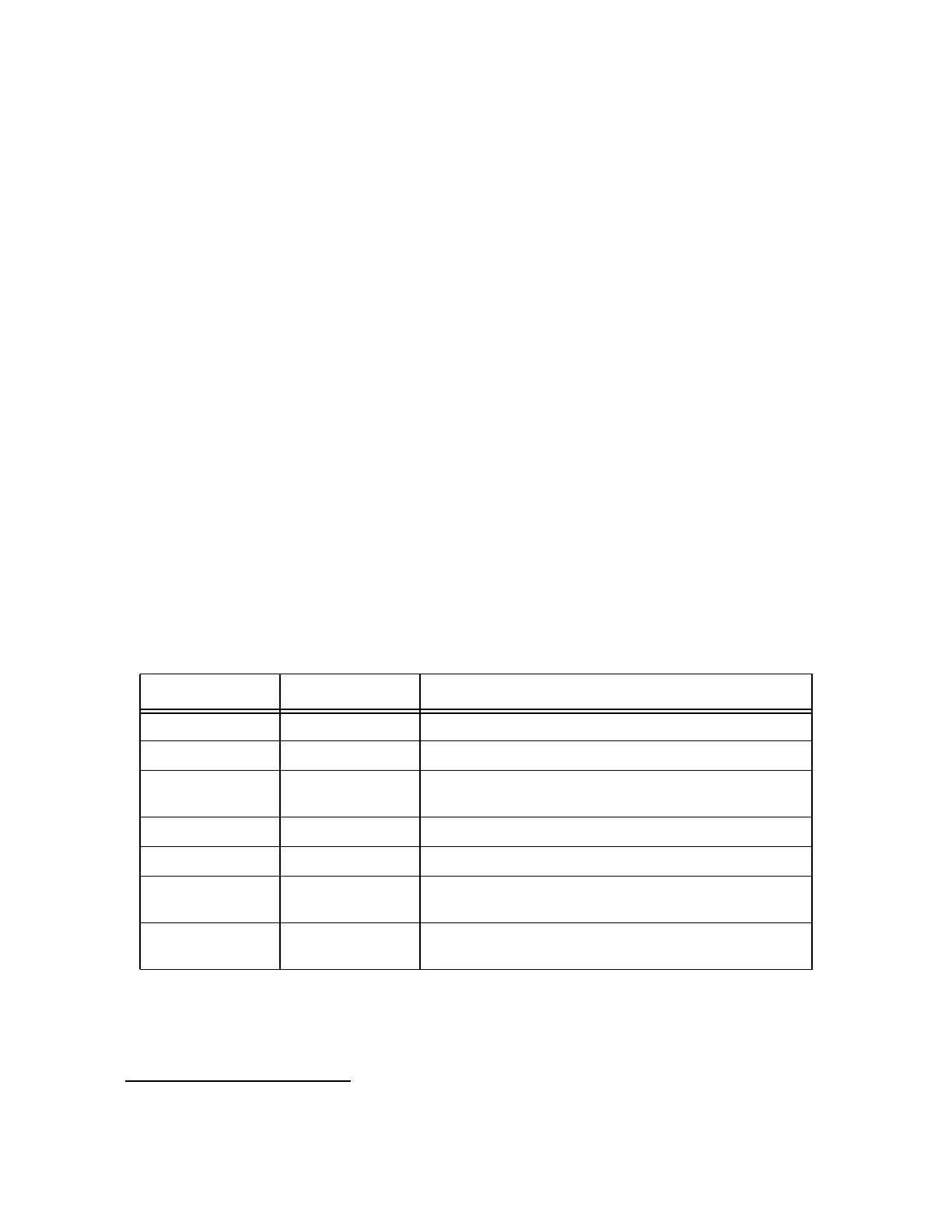

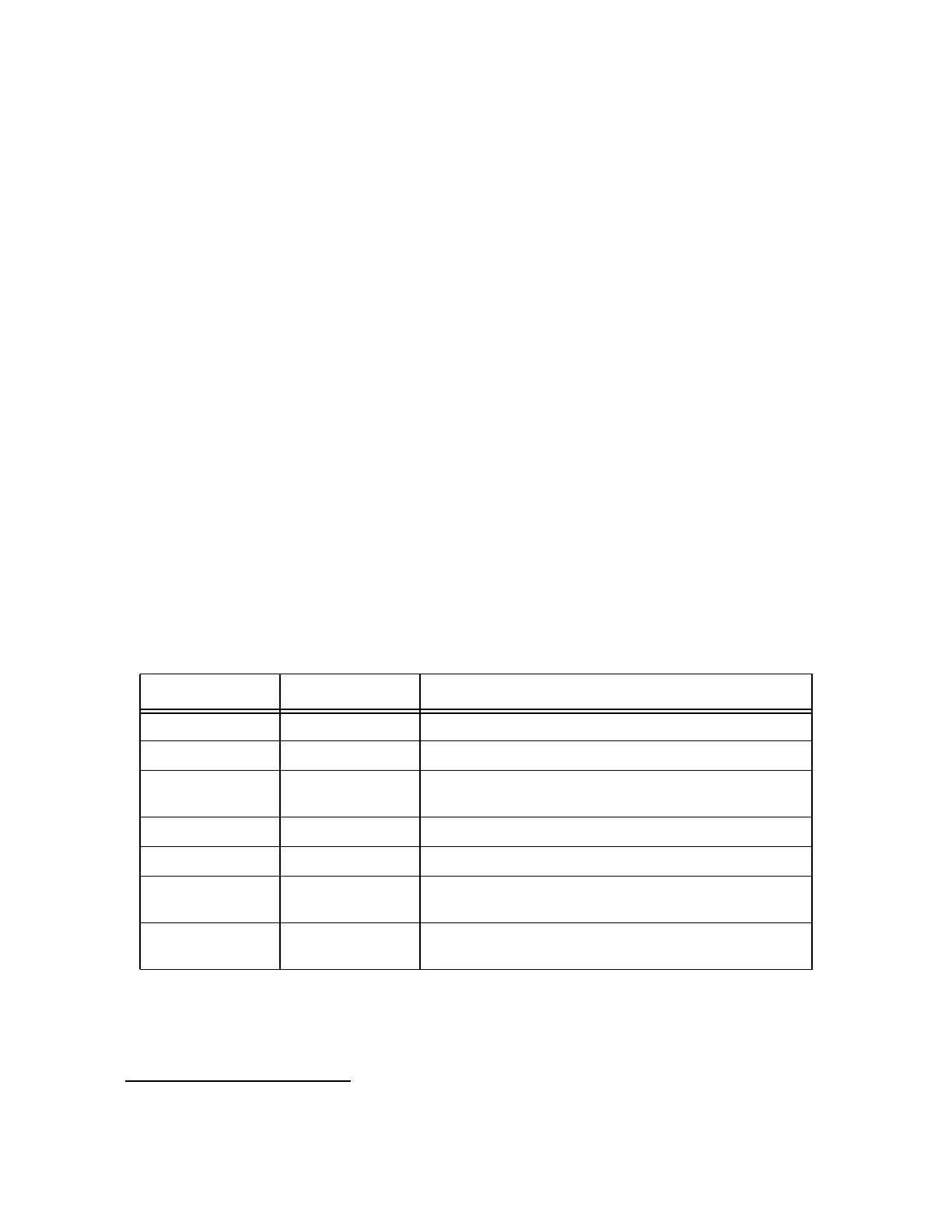

Table 6.1 Basic Addressing Modes

MODE MNEMONIC OPERANDS

Register R operand(s) in register (in Register file)

Indirect [R] Byte/Word whose 16-bit address is in R

Indirect-Offset [R+off 8/16] Byte or Word data whose address (16-bit) contained in R, is

offset by 8/16-bit signed integer “off 8/16’

Direct mem_addr Byte/Word at given memory “mem_addr’

SFR

1

1. This is a special case of direct addressing mode but separately identified, as SFR space is sepa-

rate from data memory.

sfr_addr Byte/Word at “sfr_addr’ address

Immediate #data 4/5

#data 8/16

Immediate 4/5 and 8/16-bit integer constants “data8/16”

Bit bit 10-bit address field specifying Register File, Data Memory or

SFR bit address space

Loading...

Loading...