Intel387

TM

SX MATH COPROCESSOR

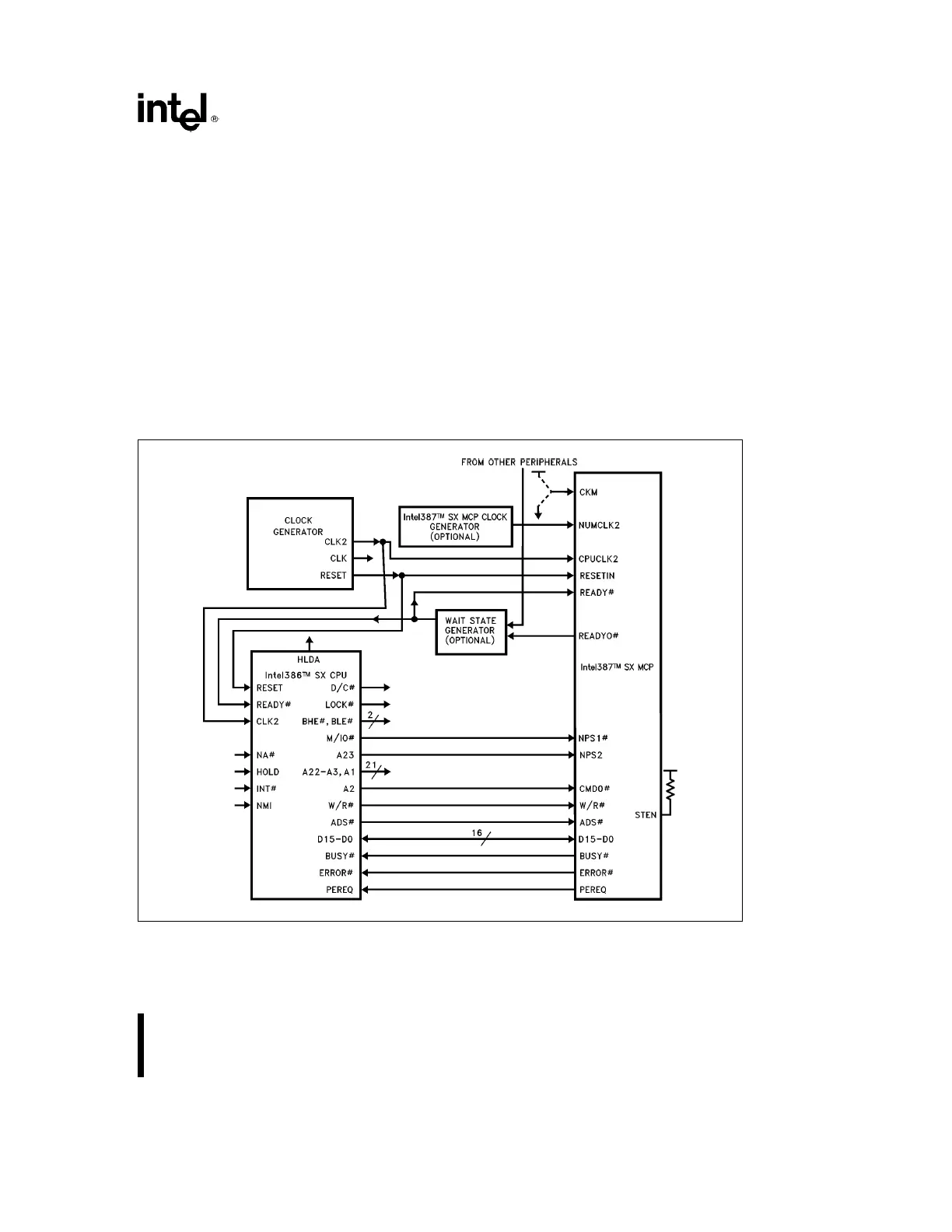

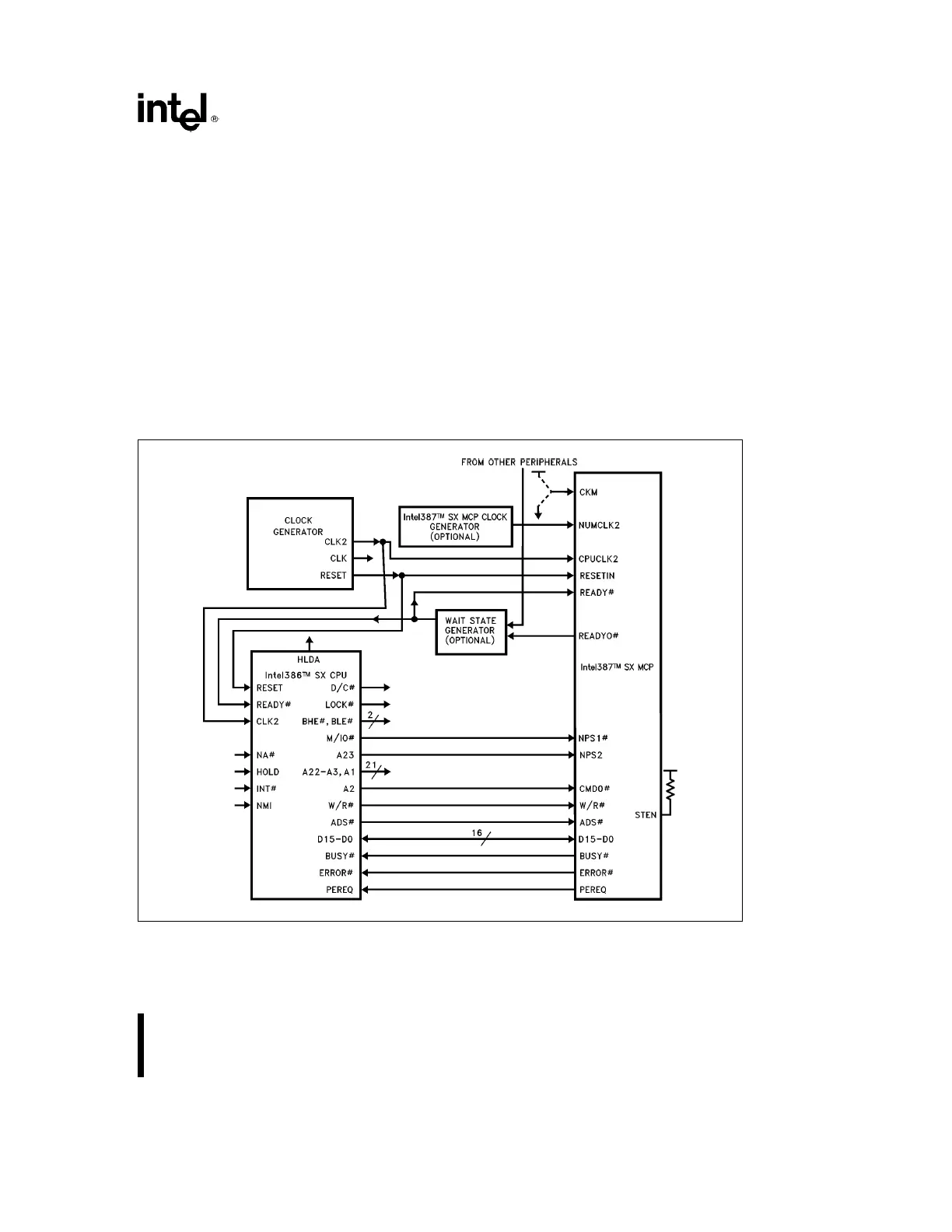

4.2 System Configuration

The Intel387 SX Math CoProcessor is designed to

interface with the Intel386 SX Microprocessor as

shown by Figure 4-1. A dedicated communication

protocol makes possible high-speed transfer of op-

codes and operands between the CPU and Math

CoProcessor. The Intel387 SX Math CoProcessor is

designed so that no additional components are re-

quired for interface with the CPU. Most control pins

of the Math CoProcessor are connected directly to

pins of the CPU.

The interface between the Math CoProcessor and

the CPU has these characteristics:

#

The Math CoProcessor shares the local bus of

the Intel386 SX Microprocessor.

#

The CPU and Math CoProcessor share the same

reset signals. They may also share the same

clock input; however, for greatest performance,

an external oscillator may be needed.

#

The corresponding Busy

Ý

, ERROR

Ý

, and

PEREQ pins are connected together.

#

The Math CoProcessor NPS1

Ý

and NPS2 inputs

are connected to the latched CPU M/IO

Ý

and

A23 outputs respectively. For Math CoProcessor

cycles, M/IO

Ý

is always LOW and A23 always

HIGH.

#

The Math CoProcessor input CMD0 is connected

to the latched A

2

output. The Intel386 SX Micro-

processor generates address 8000F8H when

writing a command and address 8000FCH or

8000FEH (treated as 8000FCH by the Intel387

SX Math CoProcessor) when writing or reading

data. It does not generate any other addresses

during Math CoProcessor bus cycles.

240225–6

Figure 4-1. Intel386

TM

SX CPU and Intel387

TM

SX Math CoProcessor System Configuration

25

25

Loading...

Loading...