3/24/97 2-6 Architectural Overview

because each has a different set of peripheral functions. Many SFR addresses will be unused on

any particular XA derivative.

The first 64 bytes of on-chip SFR space are bit-addressable. Any CPU or peripheral register that

allows bit access will be allocated an address within that range.

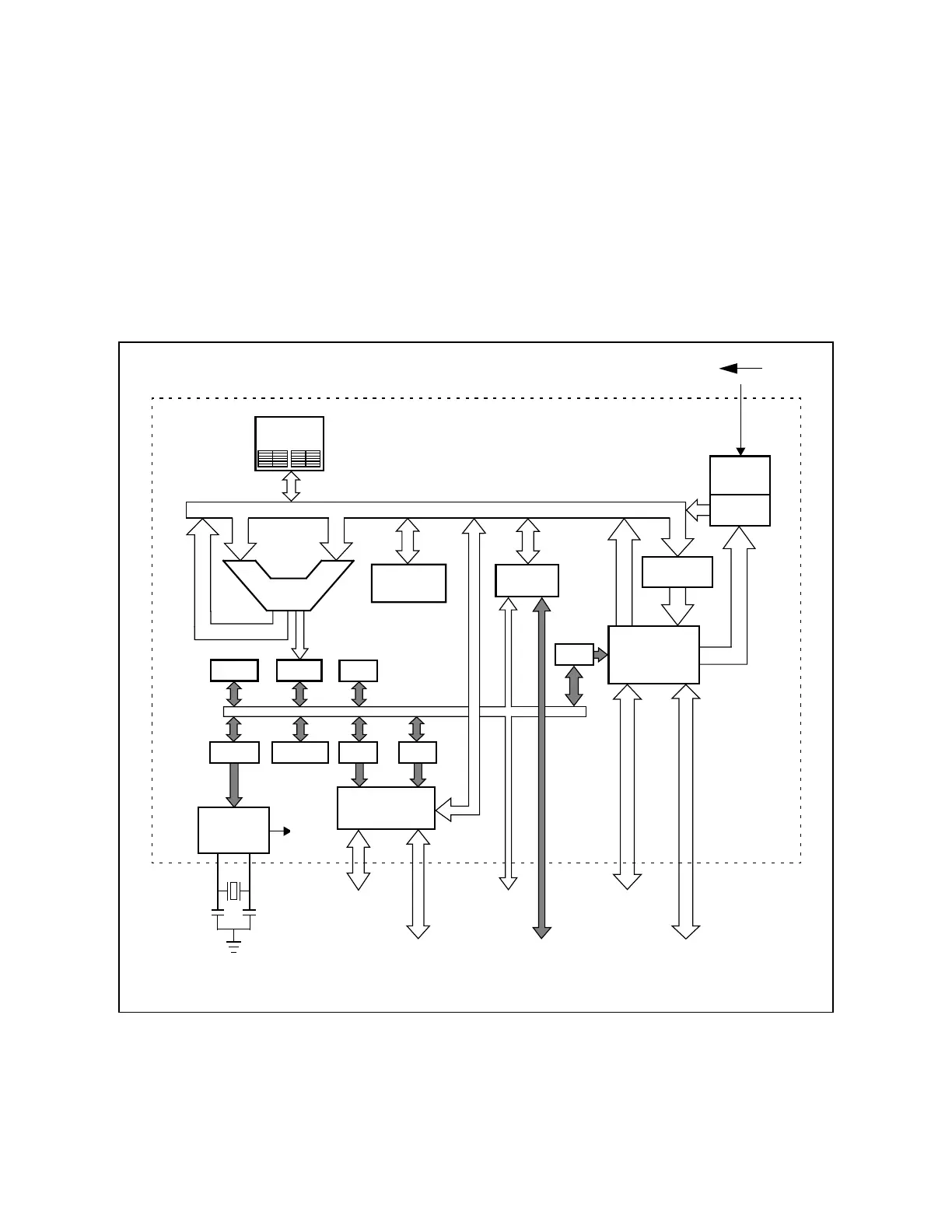

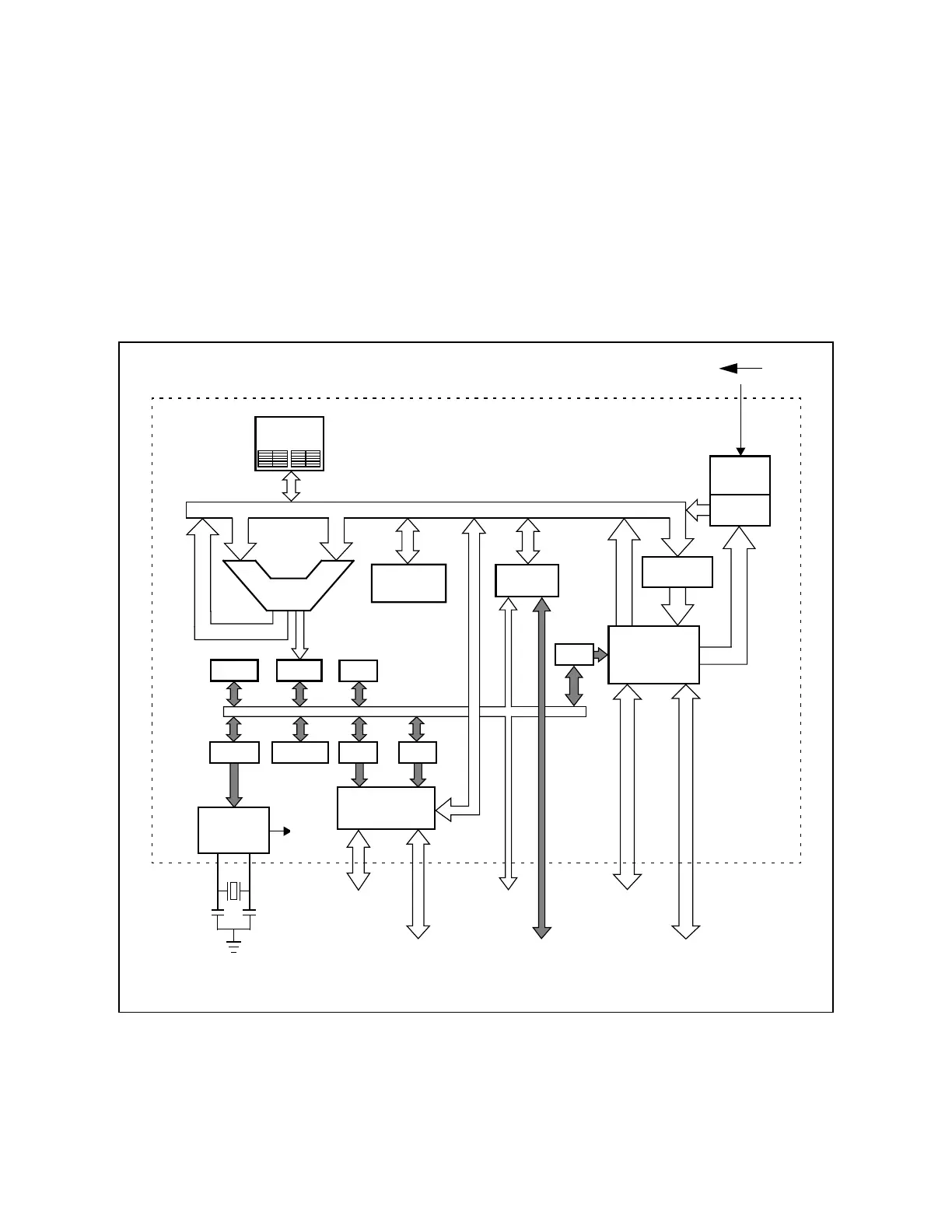

2.3 CPU

Figure 2.6 shows the XA architecture as a whole. Each of the blocks shown are described in this

section.

Figure 2.6 The XA Architecture

SFR bus

interface

Exception

Controller

Program

Counter

On-chip

Peripherals

On-chip

EPROM/

ROM

PSWL

PSWH

SCR

SSELPCON ES DS

Data/Address/Control Bus

RESET

Oscillator

16-bit

CS

External

Program

Memory

External

Data

Memory

On-chip

RAM

Program

Memory

Interface

ALU

16-bit

Data Memory

Interface

External

SFR

Devices

Register

File

Execution

Unit

IREG

CPU

Clock

SFR bus

8 or 16 bits

Loading...

Loading...